### VEMU INSTITUTE OF TECHNOLOGY

Permanently Affiliated to JNTUA, Approved by AICTE

Accredited by NAAC, Bangalore

Three B.Tech Programmes ( CSE, ECE & EEE ) are accredited by NBA, New Delhi ACCREDITED as A - GRADE By GOVT. of A.P. DEPARTMENT OF TECHNICAL EDUCATION Recognized under 2(F) & 12(B) UGC ACT An ISO 9001:2015 Certified Institution

## (20A04503T) MICROPROCESSORS AND MICROCONTROLLERS

Dr.G.ELAIYARAJA.,M.E.Ph.D

**Professor**

**Department of ECE**

**VEMU Institute of Technology,**

P.Kothakota, Chittoor, AP.

## Course Objectives:

- To introduce fundamental architectural concepts of microprocessors and microcontrollers.

- To impart knowledge on addressing modes and instruction set of 8086 and 8051

- To introduce assembly language programming concepts

- To explain memory and I/O interfacing with 8086 and 8051

- To introduce 16 bit and 32 bit microcontrollers.

## **Course Outcomes:**

| CO  | Description                                                                        | Blooms |

|-----|------------------------------------------------------------------------------------|--------|

|     |                                                                                    | Level  |

| CO1 | Explain about the 8086 microprocessor architecture and its pin diagram description | 02     |

| CO2 | Develop the assembly language programming concepts using 8086 instruction sets     | 03     |

| CO3 | Explain the interfacing of 8086 microprocessor with peripheral devices             | 02     |

| CO4 | Explain the architecture and instruction set of 8051 microcontroller               | 02     |

| CO5 | Design the applications using 8051 microcontrollers                                | 06     |

\*8086 Architecture:

Main features, pin diagram/description, 8086 microprocessor family, internal architecture, bus interfacing unit, execution unit, interrupts and interrupt response, 8086 system timing, minimum mode and maximum mode configuration.

\*8086 Programming:

Program development steps, instructions, addressing modes, assembler directives, writing simple programs with an assembler, assembly language program development tools.

### \*8086 Interfacing:

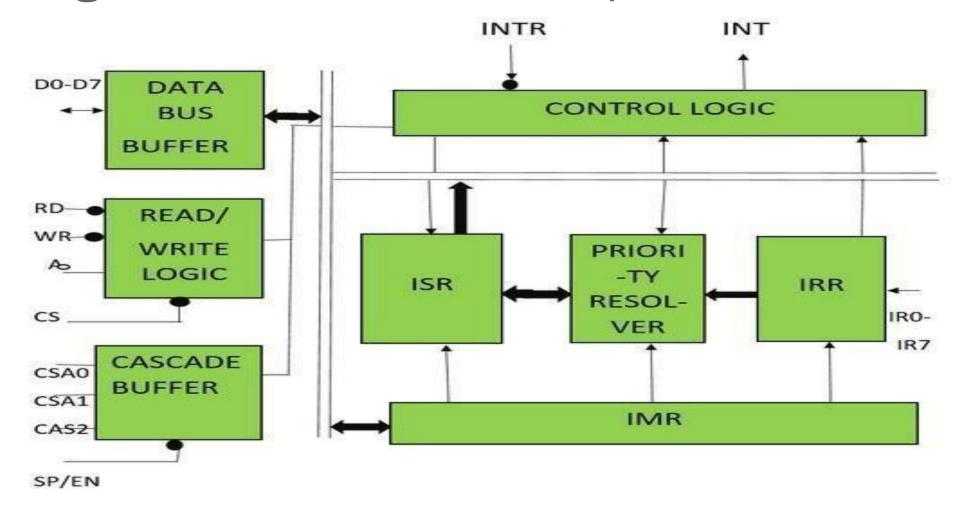

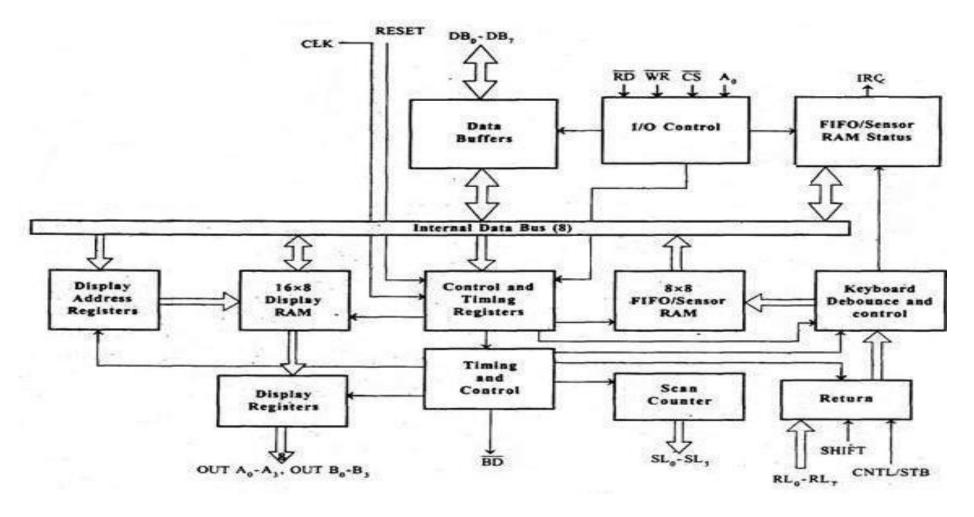

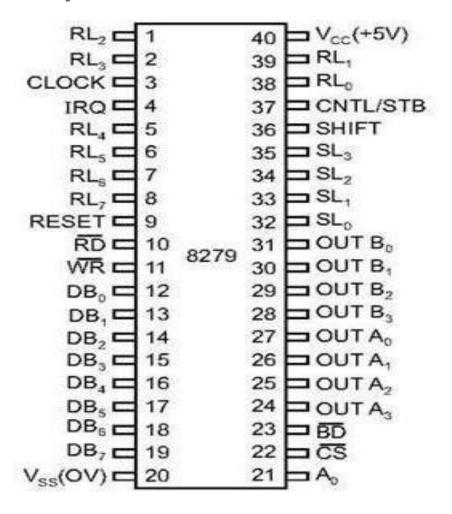

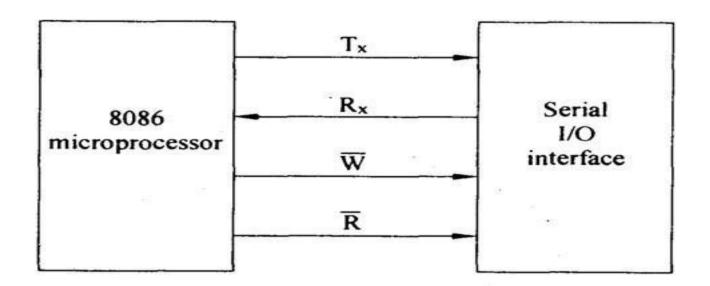

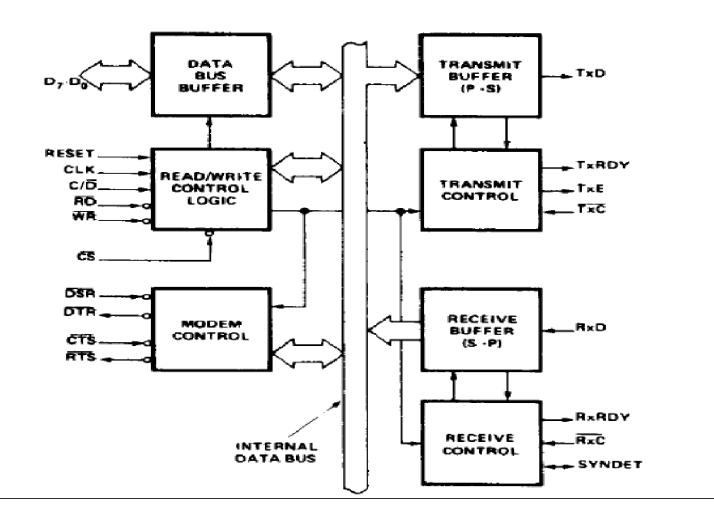

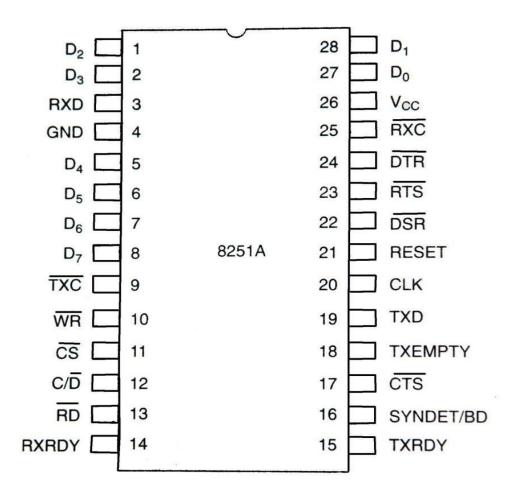

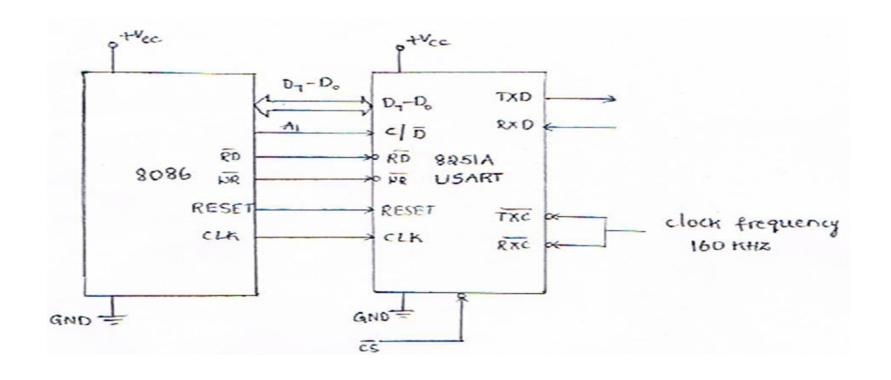

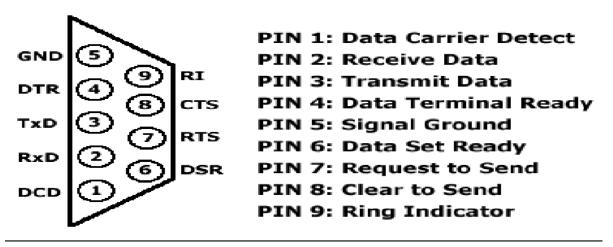

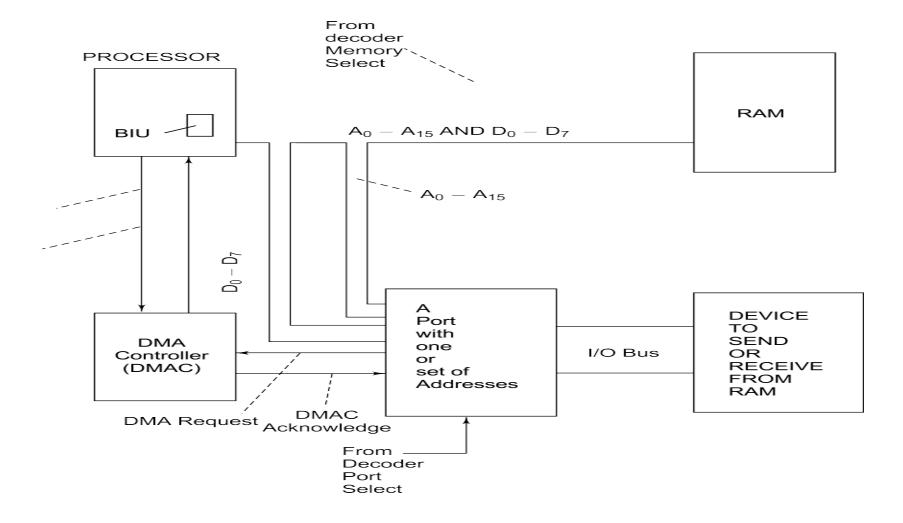

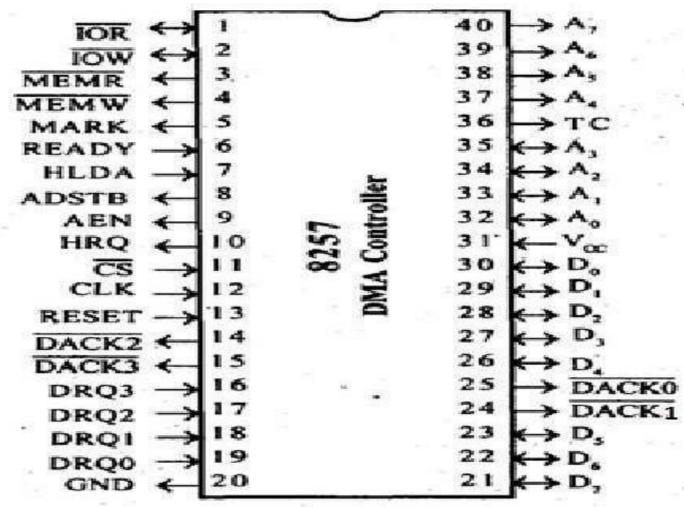

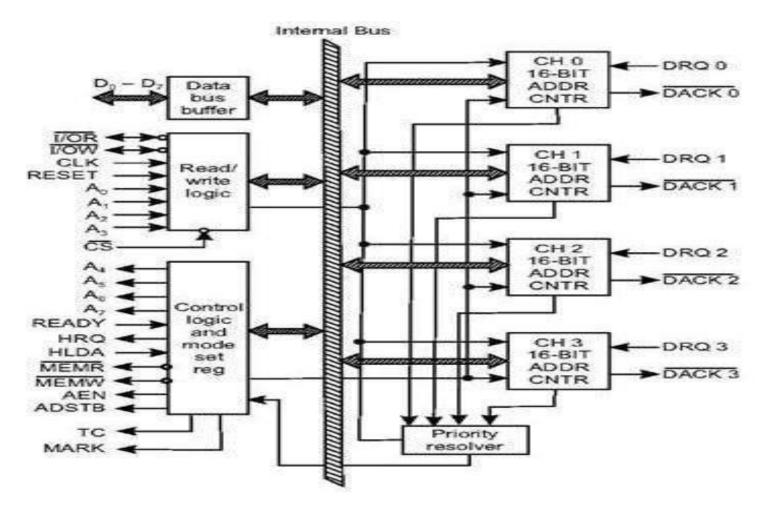

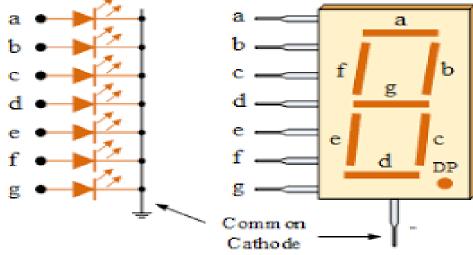

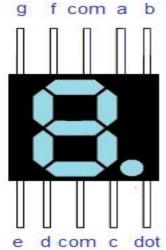

Semiconductor memories interfacing (RAM, ROM), Intel 8255 programmable peripheral interface, Interfacing switches and LEDS, Interfacing seven segment displays, software and hardware interrupt applications, Intel 8251 USART architecture and interfacing, Intel 8237a DMA controller, stepper motor, A/D and D/A converters, Need for 8259 programmable interrupt controllers.

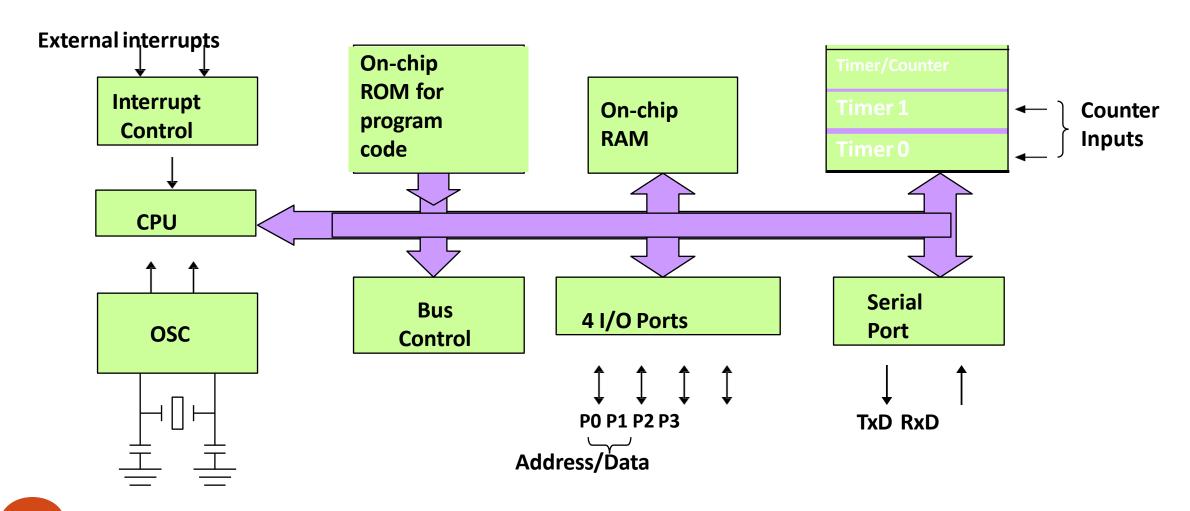

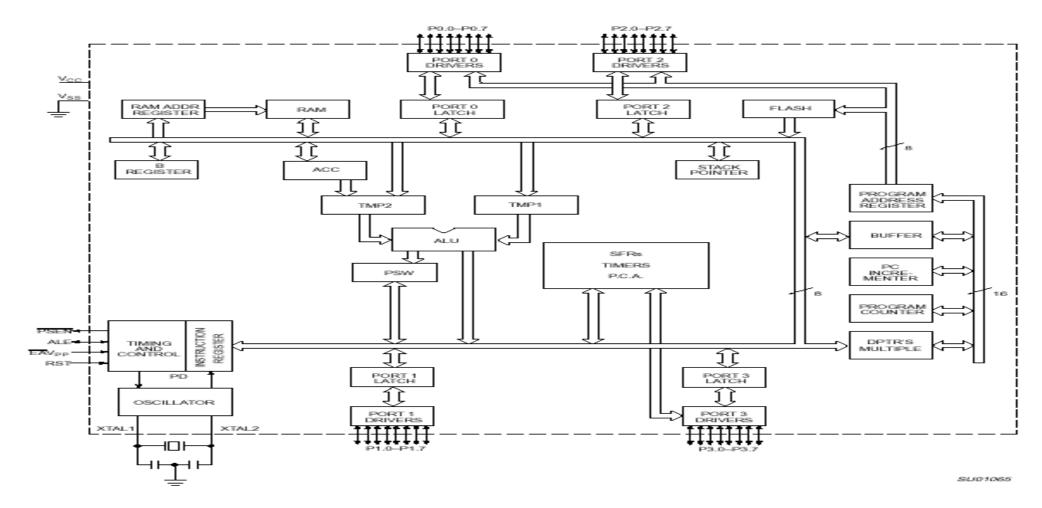

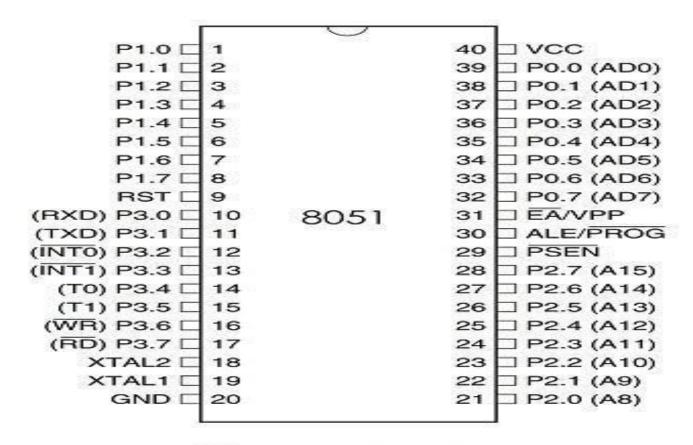

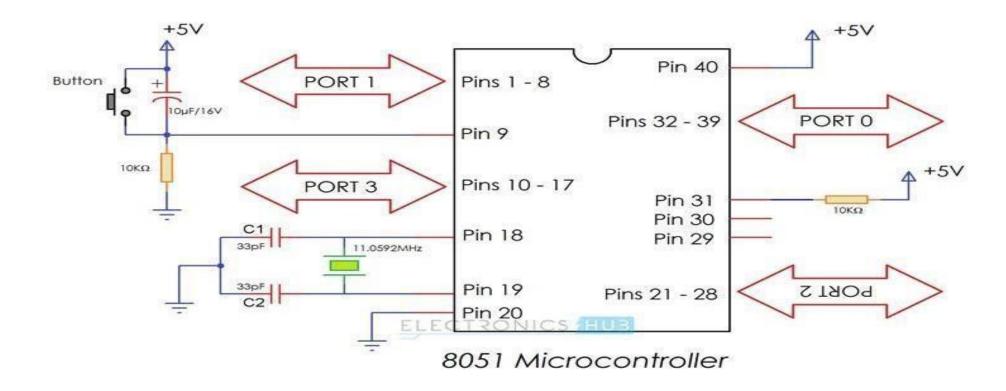

❖Microcontroller - Architecture of 8051 — Special Function Registers(SFRs) - I/O Pins Ports and Circuits - Instruction set - Addressing modes - Assembly language programming.

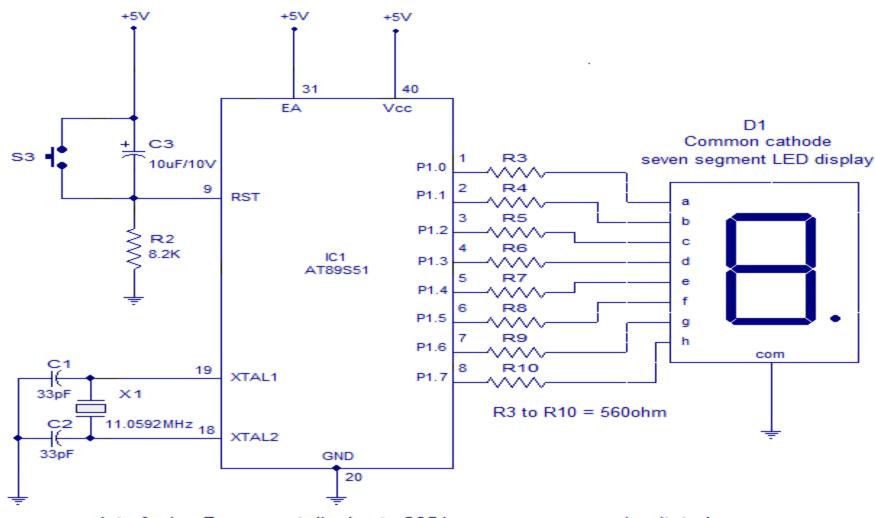

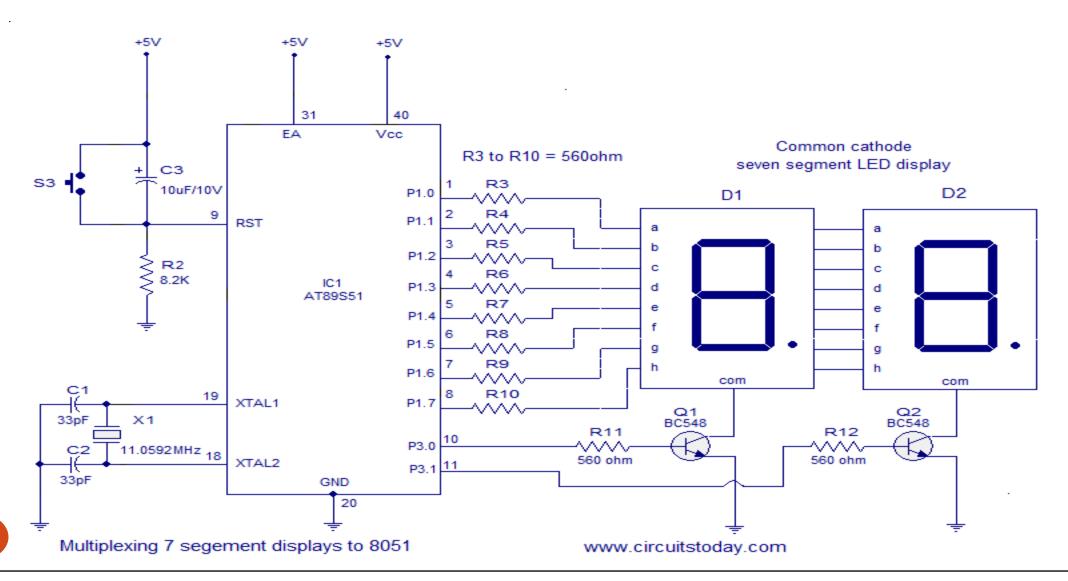

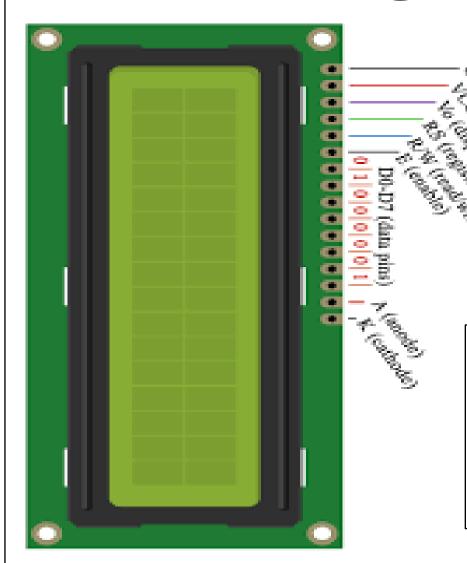

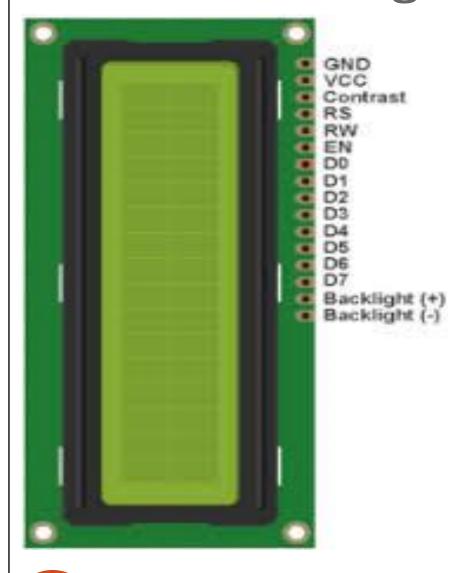

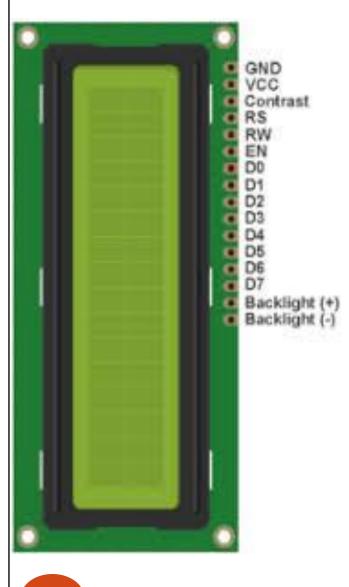

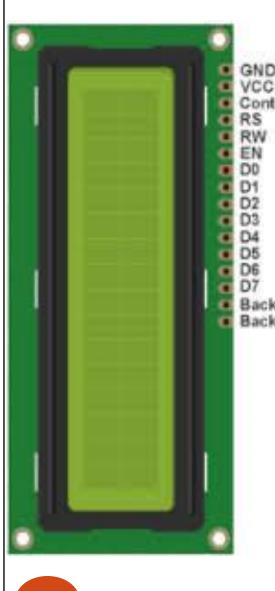

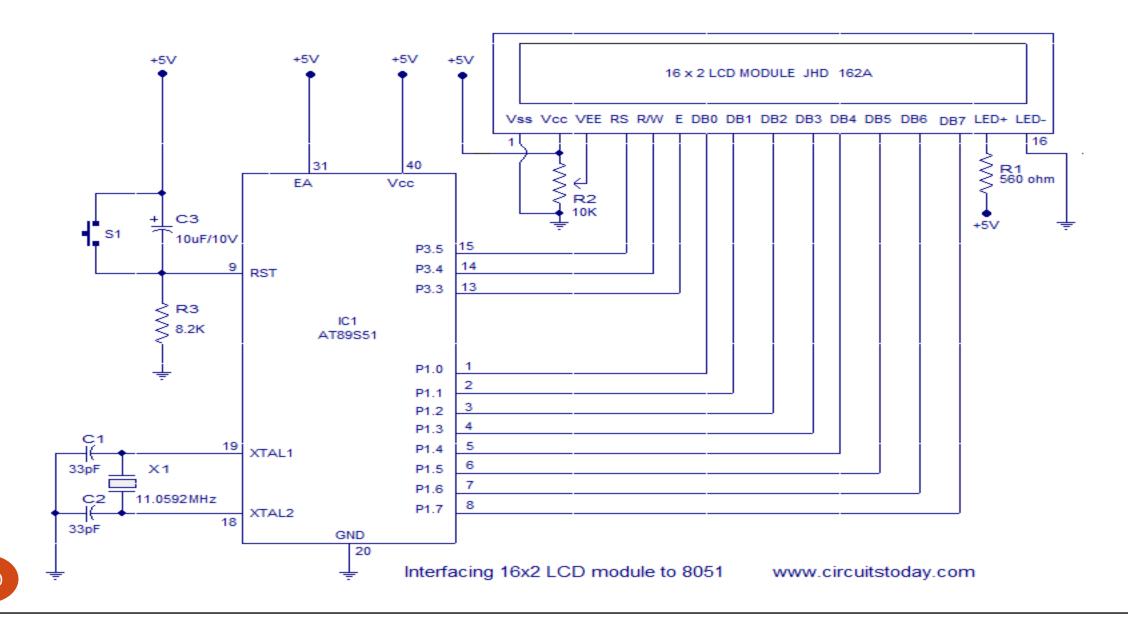

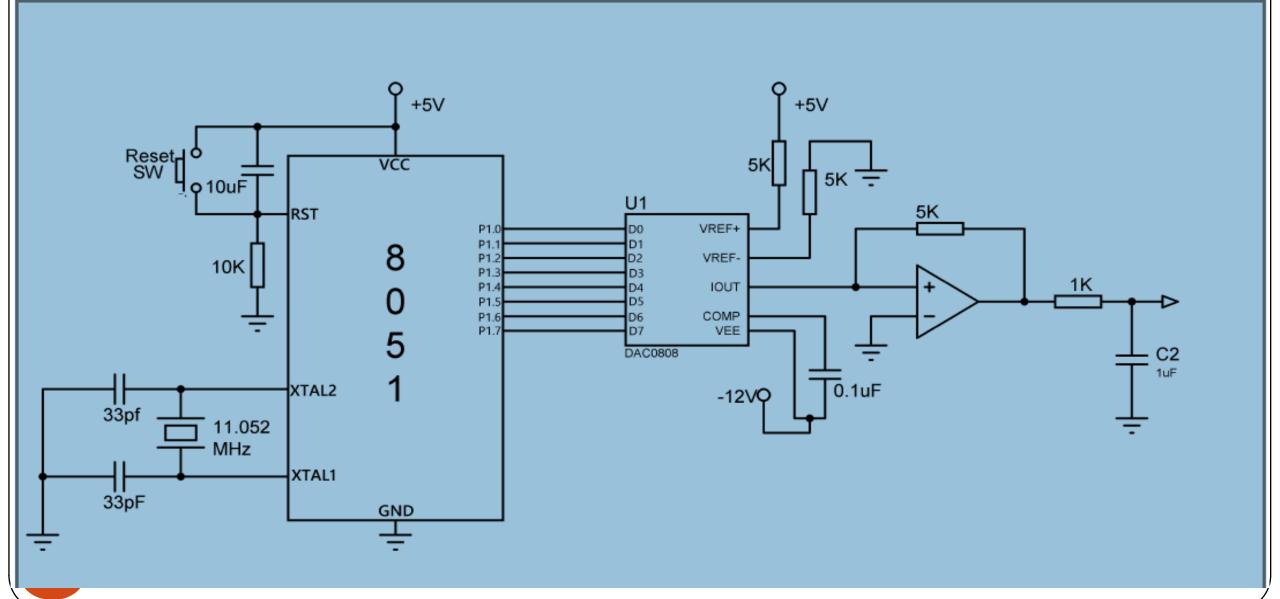

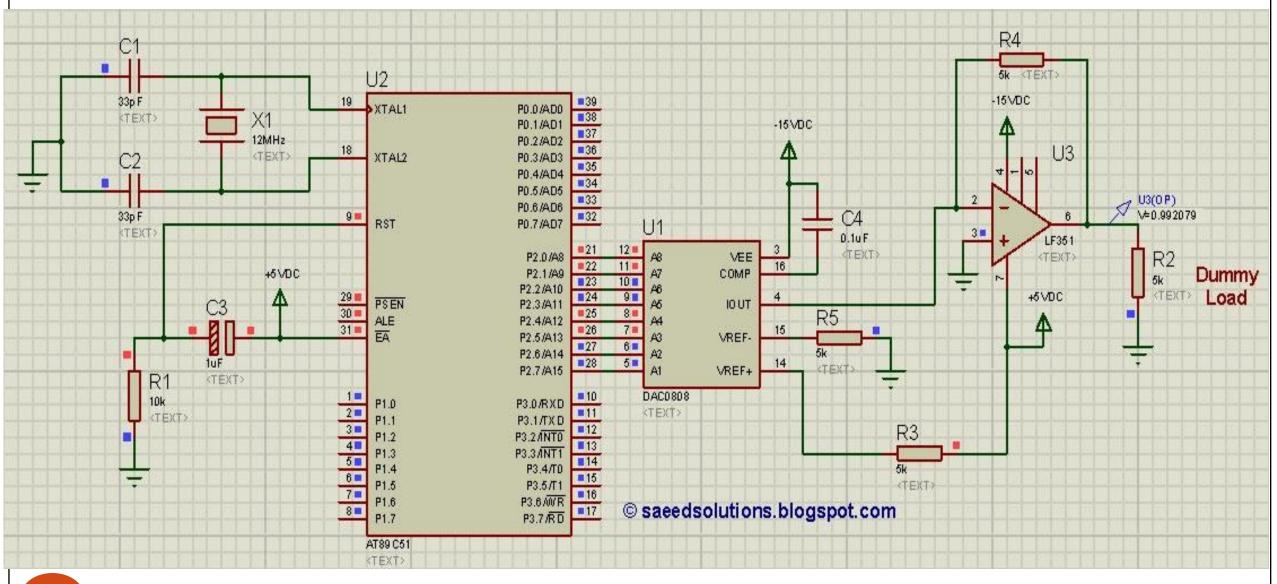

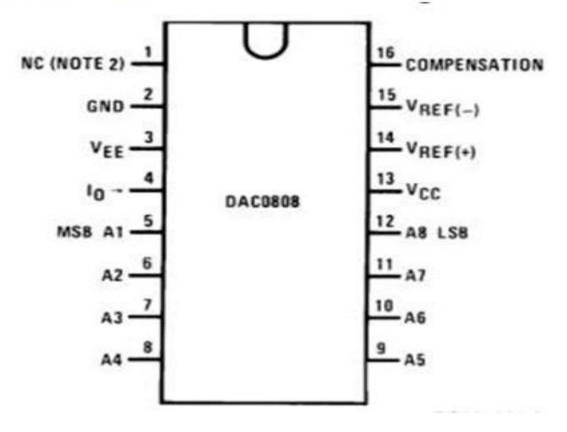

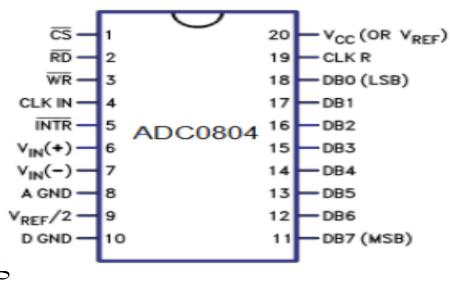

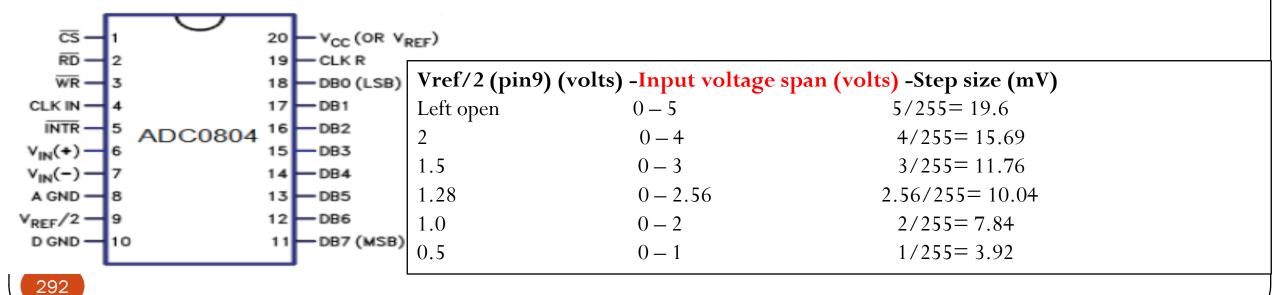

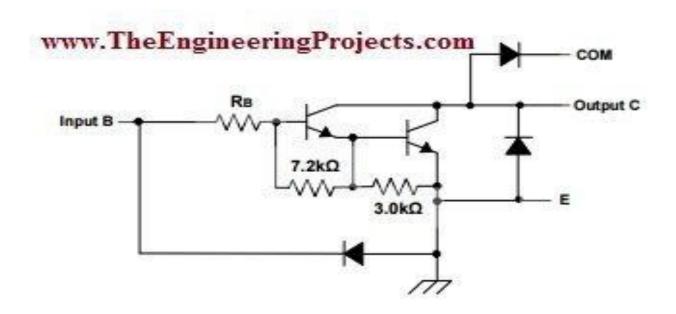

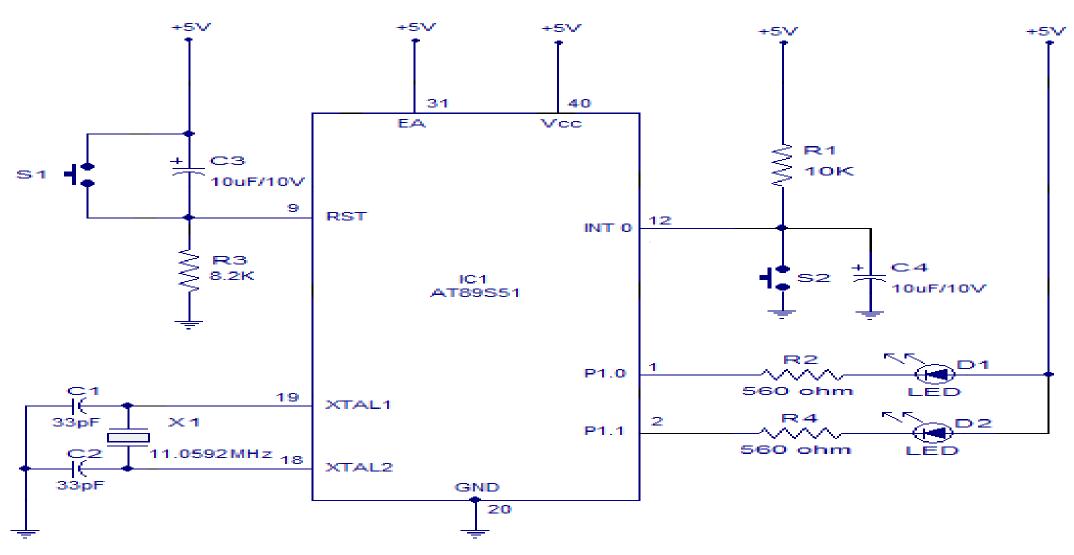

❖ Interfacing Microcontroller - Programming 8051 Timers - Serial Port Programming - Interrupts Programming — LCD & Keyboard Interfacing - ADC, DAC & Sensor Interfacing - External Memory Interface- Stepper Motor and Waveform generation - Comparison of Microprocessor, Microcontroller, PIC and ARM processors

## Textbooks& References

### • Textbooks:

- 1. Microprocessors and Interfacing Programming and Hardware by Douglas V Hall, SSSP Rao, Tata McGraw Hill Education Private Limited, 3rdEdition, 1994.

- 2. K M Bhurchandi, A K Ray, Advanced Microprocessors and Peripherals, 3rd edition, McGraw Hill Education, 2017.

- 3. Raj Kamal, Microcontrollers: Architecture, Programming, Interfacing and System Design, 2nd edition, Pearson, 2012.

#### • References:

- 1. Ramesh S Gaonkar, Microprocessor Architecture Programming and Applications with the 8085, 6th edition, Penram International Publishing, 2013.

- 2. Kenneth J. Ayala, The 8051 Microcontroller, 3rd edition, Cengage Learning, 2004.

## Introduction to processor:

- A processor is the logic circuitry that responds to and processes the basic instructions that drives a computer.

- The term processor has generally replaced the term central processing unit. The processor in a personal computer or embedded in small devices is often called a microprocessor.

- The processor (CPU, for Central Processing Unit) is the computer's brain. It allows the

processing of numeric data, meaning information entered in binary form, and the

execution of instructions stored in memory.

- A microprocessor is used as the CPU in a microcomputer. There are now many different microprocessors available.

- Microprocessor is a program-controlled device, which fetches the instructions from memory, decodes and executes the instructions. Most Micro Processor are singlechip devices.

- Microprocessor is a backbone of computer system. which is called CPU

- Microprocessor speed depends on the processing speed depends on DATA BUS WIDTH.

- A common way of categorizing microprocessors is by the no. of bits that their ALU can Work with at a time

- The address bus is unidirectional because the address information is always given by the Micro Processor to address a memory location of an input / output devices.

- ➤ The data bus is Bi-directional because the same bus is used for transfer of data between Micro Processor and memory or input / output devices in both the direction.

- ➤ It has limitations on the size of data. Most Microprocessor does not support floating-point operations.

- ➤ Microprocessor contain ROM chip because it contain instructions to execute data.

- > Storage capacity is limited. It has a volatile memory. In secondary storage device the storage capacity is larger. It is a nonvolatile memory.

Primary devices are: RAM (Read / Write memory, High Speed, Volatile Memory) / ROM (Read only memory, Low Speed, Non Volatile Memory)

### **Compiler:**

➤ Compiler is used to translate the high-level language program into machine code at a time. It doesn't require special instruction to store in a memory, it stores automatically. The Execution time is less compared to Interpreter

### RISC (Reduced Instruction Set Computer):

- RISC stands for Reduced Instruction Set Computer. To execute each instruction, if there is separate

- electronic circuitry in the control unit, which produces all the necessary signals, this

approach of the design of the control section of the processor is called RISC design. It is also

called hardwired approach.

### **Examples of RISC processors:**

- IBM RS6000, MC88100

- DEC's Alpha 21064, 21164 and 21264 processors

## Features of RISC Processors:

- The standard features of RISC processors are listed below:

- RISC processors use a small and limited number of instructions.

- RISC machines mostly uses hardwired control unit.

- RISC processors consume less power and are having high performance.

- Each instruction is very simple and consistent.

- RISC processors uses simple addressing modes.

- RISC instruction is of uniform fixed length

## Features of RISC Processors:

### **CISC (Complex Instruction Set Computer):**

CISC stands for Complex Instruction Set Computer. If the control unit contains a number of microelectronic circuitry to generate a set of control signals and each micro circuitry is activated by a micro code, this design approach is called CISC design.

### **Examples of CISC processors are:**

- Intel 386, 486, Pentium, Pentium Pro, Pentium II, Pentium III

- Motorola's 68000, 68020, 68040, etc.

## Features of CISC Processors:

- CISC chips have a large amount of different and complex instructions.

- CISC machines generally make use of complex addressing modes.

- > Different machine programs can be executed on CISC machine.

- CISC machines uses micro-program control unit.

- CISC processors are having limited number of registers

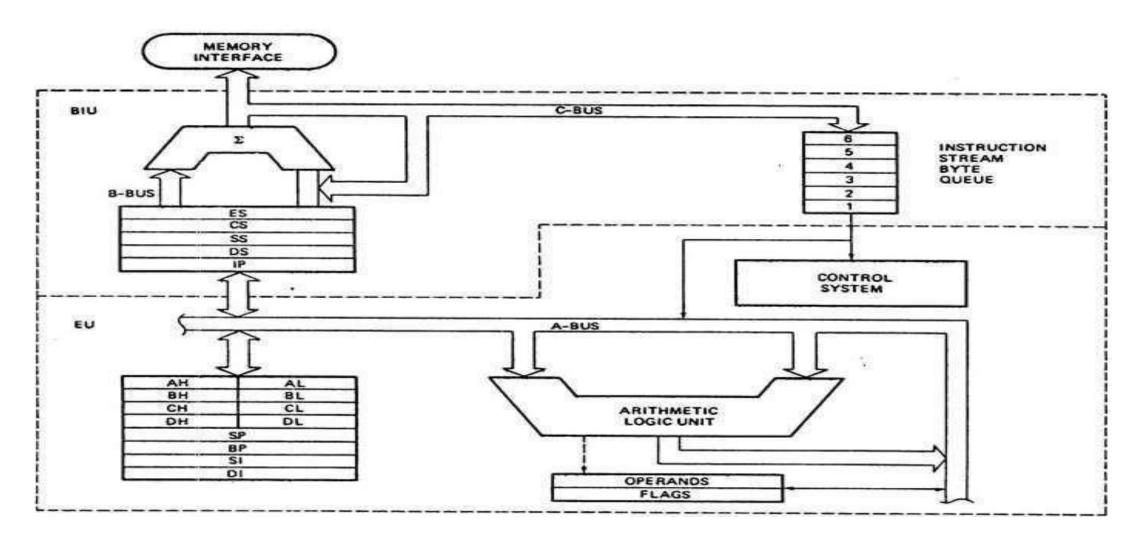

8086 Microprocessor is divided into two functional units, i.e., **EU**(Execution Unit) and **BIU** (Bus Interface Unit).

### **EU** (Execution Unit):

Execution unit gives instructions to BIU stating from where to fetch the data and then decode and execute those instructions. Its function is to control operations on data using the instruction decoder & ALU. EU has no direct connection with system buses as shown in the above figure, it performs operations over data through BIU.

### **BIU(Bus Interface Unit):**

➤ BIU takes care of all data and addresses transfers on the buses for the EU like sending addresses, fetching instructions from the memory, reading data from the ports and the memory as well as writing data to the ports and the memory. EU has no direction connection with System Buses so this is possible with the BIU. EU and BIU are connected with the Internal Bus.

### **Instruction queue:**

➤ BIU contains the instruction queue. BIU gets up to 6 bytes of next instructions and stores them in the instruction queue. When EU executes instructions and is ready for its next instruction, then it simply reads the instruction from this instruction queue resulting in increased execution speed.

### Segment register:

➤ BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations. It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

# Special functions of general purpose register

### **AX & DX registers:**

- In 8 bit multiplication, one of the operands must be in AL. The other operand can be a byte in memory location or in another 8 bit register. The resulting 16 bit product is stored in AX, with AH storing the MS byte.

- In 16 bit multiplication, one of the operands must be in AX.

- The other operand can be a word in memory location or in another 16 bit register. The resulting 32 bit product is stored in DX and AX, with DX storing the MS word and AX storing the LS word.

# special functions of general purpose register

### **BX** register:

In instructions where we need to specify in a general purpose register the 16 bit effective address of a memory location, the register BX is used (register indirect).

#### **CX** register:

In Loop Instructions, CX register will be always used as the implied counter. In I/O instructions, the 8086 receives into or sends out data from AX or AL depending as a word or byte operation.

# Segment register:

### Segment register:

➤ BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations. It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

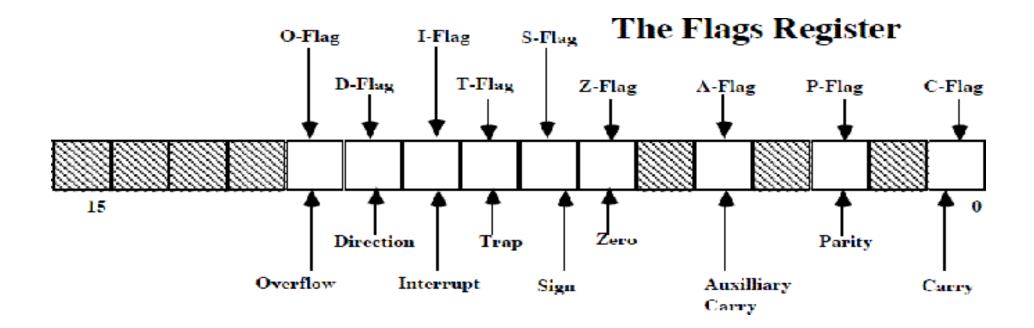

- Flag Register contains a group of status bits called flags that indicate the status of the CPU or the result of arithmetic operations.

- There are two types of flags:

- The **status flags** which reflect the result of executing an instruction. The programmer cannot set/reset these flags directly.

- The **control flags** enable or disable certain CPU operations.

- $\blacktriangleright$  The programmer can set/reset these bits to control the CPU's operation.

Nine individual bits of the status register are used as control flags (3 of them) and status flags (6 of them). The remaining 7 are not used.

A flag can only take on the values 0 and 1. We say a flag is set if it has the value 1. The status flags are used to record specific characteristics of arithmetic and of logical instructions.

# Structure of Flag Register

- **Control Flags:** There are three control flags

- The Direction Flag (D): Affects the direction of moving data blocks by such

- instructions as MOVS, CMPS and SCAS. The flag values are 0 = up and 1 = down and can be set/reset by

- the STD (set D) and CLD (clear D) instructions.

- **The Interrupt Flag (I):** Dictates whether or not system interrupts can occur. Interrupts are actions initiated by hardware block such as input devices that will interrupt the normal execution of programs.

- The flag values are 0 = disable interrupts or 1 = enable interrupts and can be manipulated by the CLI (clear I) and STI (set I) instructions.

- The Trap Flag (T): Determines whether or not the CPU is halted after the execution of each instruction. When this flag is set (i.e. = 1), the programmer can single step through his program to debug any errors. When this flag = 0 this feature is off. This flag can be set by the INT 3 instruction.

- **Status Flags:** There are six status flags

- The Carry Flag (C): This flag is set when the result of an unsigned arithmetic operation is too large to fit in the destination register. This happens when there is an end carry in an addition operation or there an end borrows in a subtraction operation. A value of 1 = carry and 0 = no carry.

The Overflow Flag (O): This flag is set when the result of a signed arithmetic operation is too large to fit in the destination register (i.e. when an overflow occurs). Overflow can occur when adding two numbers with the same sign (i.e. both positive or both negative). A value of 1 = overflow and 0 = no overflow.

**The Sign Flag (S):** This flag is set when the result of an arithmetic or logic operation is negative. This flag is a copy of the MSB of the result (i.e. the sign bit). A value of 1 means negative and 0 = positive.

**The Zero Flag (Z):** This flag is set when the result of an arithmetic or logic operation is equal to zero. A value of 1 means the result is zero and a value of 0 means the result is not zero.

**The Auxiliary Carry Flag (A):** This flag is set when an operation causes a carry from bit 3 to bit 4 (or a borrow from bit 4 to bit 3) of an operand. A value of 1 = carry and 0 = no carry.

**The Parity Flag (P):** This flags reflects the number of 1s in the result of an operation. If the number of 1s is even its value = 1 and if the number of 1s is odd then its value = 0.

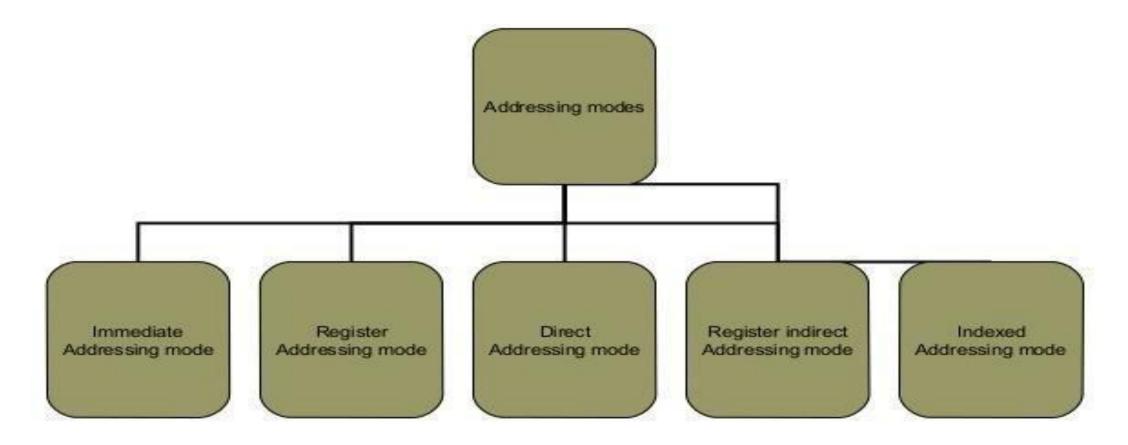

Addressing mode indicates a way of locating data or operands. Depending up on the data type used in the instruction and the memory addressing modes, any instruction may belong to one or more addressing modes or same instruction may not belong to any of the addressing modes.

The addressing mode describes the types of operands and the way they are

accessed for executing an instruction. According to the execution, the instructions may be categorized as

- Sequential control flow instructions and

- Control transfer instructions.

flow of instruction

- Sequential control flow instructions are the instructions which after execution, transfer control to the

next instruction appearing immediately after it (in the sequence) in the program. For example the

arithmetic, logic, data transfer and processor control instructions are Sequential control flow

instructions.

- The control transfer instructions on the other hand transfer control to some predefined address or the address somehow specified in the instruction, after their execution. For example INT, CALL, RET & JUMP instructions fall under this category.

- ➤ The addressing modes for Sequential and control flow instructions are explained as follows.

- > Immediate addressing mode:

- In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes.

- > Example: MOV AX, 0005H.

- ➤ In the above example, 0005H is the immediate data. The immediate may be 8- bit or 16-bit in size.

data

#### **Direct addressing mode:**

• In the direct addressing mode, a 16-bit memory address (offset) directly specified in the instruction as a part of it.

Example: MOV AX, [5000H].

### **Register addressing mode:**

In the register addressing mode, the data is stored in a register and

referred using the particular register. All the registers, except IP,

may be

used in this mode.

Example: MOV BX, AX

### Register indirect addressing mode:

• Sometimes, the address of the memory location which contains data or operands is determined in an indirect way, using the offset registers. The mode of addressing is known as register indirect mode.

• In this addressing mode, the offset address of data is in either BX or SI or DI Register. The default segment is either DS or ES.

**Example:** MOV AX, [BX].

### **Indexed addressing mode:**

• In this addressing mode, offset of the operand is stored one of the index registers. DS & ES are the default segments for index registers SI & DI respectively.

Example: MOV AX, [SI]

Here, data is available at an offset address stored in SI in DS.

### Register relative addressing mode:

• In this addressing mode, the data is available at an effective address formed by adding an 8-bit or 16-bit displacement with the content of any one of the register BX, BP, SI & DI in the default (either in DS & ES) segment.

Example: MOV AX, 50H [BX]

### Based indexed addressing mode:

The effective address of data is formed in this addressing mode, by adding content of a base register (any one of BX or BP) to the content of an index register (any one of SI or DI). The default segment register may be ES or DS. **Example:** MOV AX, [BX][SI]

#### Relative based indexed:

The effective address is formed by adding an 8 or 16-bit displacement with the sum of contents of any of the base registers (BX or BP) and any one of the index registers, in a default segment.

Example: MOV AX, 50H [BX] [SI]

### **Addressing Modes for control transfer instructions:**

### Intersegment

- Intersegment direct

- Intersegment indirect

#### Intrasegment

- Intrasegment direct

- Intrasegment indirect

### **Intersegment direct:**

In this mode, the address to which the control is to be transferred is in a different segment. This addressing mode provides a means of branching from one code segment to another code segment. Here, the CS and IP of the destination address are specified directly in the instruction.

**Example:** JMP 5000H: 2000H;

Jump to effective address 2000H in segment 5000H.

### **Intersegment indirect:**

- In this mode, the address to which the control is to be transferred lies in a different segment and it is passed to the instruction indirectly, i.e. contents of a memory block containing four bytes, i.e. IP(LSB), IP(MSB), CS(LSB) and CS(MSB) sequentially. The starting address of the memory block may be referred using any of the addressing modes, except immediate mode.

- Example: JMP [2000H].

Jump to an address in the other segment specified at effective address 2000H in DS.

### **Intrasegment direct mode:**

In this mode, the address to which the control is to be transferred lies in the same segment in which the control transfers instruction lies and appears directly in the instruction as an immediate displacement value. In this addressing mode, the displacement is computed relative to the content of the instruction pointer.

• The effective address to which the control will be transferred is given by the sum of 8 or 16 bit displacement and current content of jump instruction, if the signed displacement (d) is of 8-128<d<+127), it as short jump and if it is of 16 bits (i.e. -32768<d<+32767), it is termed as long jump.

**Example:** JMP SHORT LABEL.

IP. In case of bits (i.e. -

### • Intrasegment indirect mode:

- In this mode, the displacement to which the control is to be transferred is in the same segment in which the control transfer instruction lies, but it is passed to the instruction directly. Here, the branch address is found as the content of a register or a memory location.

- This addressing mode may be used in unconditional branch instructions.

- **Example:** JMP [BX]; Jump to effective address stored in BX.

## INSTRUCTION SET OF 8086

- The Instruction set of 8086 microprocessor is classified into 7 Types, they are:-

- Data transfer instructions

- Arithmetic& logical instructions

- Program control transfer instructions

- Machine Control Instructions

- Shift / rotate instructions

- Flag manipulation instructions

- String instructions

• Data transfer instruction, as the name suggests is for the transfer of data from memory to internal register, from internal register to memory, from one register to another register, from input port to internal register, from internal register to output port etc

#### **MOV** instruction

• It is a general purpose instruction to transfer byte or word from register to register, memory to register, register to memory or with immediate addressing.

#### **General Form:**

- MOV destination, source

- Here the source and destination needs to be of the same size, that is both 8 bit or both 16 bit.

- MOV instruction does not affect any flags.

### **Example:**-

MOV BX, 00F2H;

load the immediate number 00F2H in BX register

MOV CL, [2000H] ;Copy the 8 bit content of the memory location, at a displacement of 2000H from data segment base to the CL register

- •MOV [589H], BX; Copy the 16 bit content of BX register on to the memory location, which at a displacement of 589H from the data segment base.

- MOV DS, CX; Move the content of CX to DS

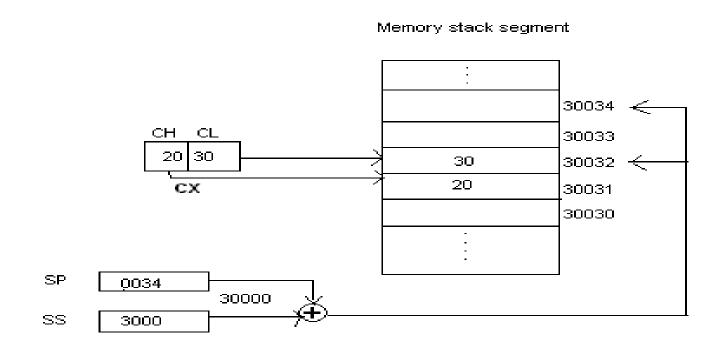

#### **PUSH** instruction

• The PUSH instruction decrements the stack pointer by two and copies the word from source to the location where stack pointer now points. Here the source must of word size data. Source can be a general purpose register, segment register or a memory location.

The PUSH instruction first pushes the most significant byte to sp-1, then the least significant to the sp-2.

Push instruction does not affect any flags.

#### **Example:**-

- PUSH CX; Decrements SP by 2, copy content of CX to the stack (figure shows execution of this instruction)

- PUSH DS ; Decrement SP by 2 and copy DS to stack

- POP instruction

The POP instruction copies a word from the stack location pointed by the stack pointer to the destination. The destination can be a General purpose register, a segment register or a memory location. Here after the content is copied the stack pointer is automatically incremented by two.

• The execution pattern is similar to that of the PUSH instruction.

#### **Example:**

• POP CX ; Copy a word from the top of the stack to CX and increment SP by 2.

- **IN & OUT instructions**

- The IN instruction will copy data from a port to the accumulator. If 8 bit is read the data will go to AL and if 16 bit then to AX. Similarly OUT instruction is used to copy data from accumulator to an output port.

- Both IN and OUT instructions can be done using direct and indirect addressing modes.

#### **Example:**

- Copy a byte from the port 0F8H to AL IN AL, OF8H;

- MOV DX, 30F8H; Copy port address in DX

- IN AL, DX;

- IN AX, DX;

- Move 8 bit data from 30F8H port Move 16 bit data OUT 047H, AL;

- MOV DX, 30F8H;Copy port address in DX Copy contents of AL to 8 bit port 047H

#### **XCHG** instruction

The XCHG instruction exchanges contents of the destination and source. Here destination

and source can be register and register or register and memory location, but XCHG cannot

interchange the value of 2 memory locations.

#### **General Format**

XCHG Destination, Source

### **Example:**

- XCHG BX, CX; exchange word in CX with the word in BX

- XCHG AL, CL; exchange byte in CL with the byte in AL

- XCHG AX, SUM[BX]; here physical address, which is DS+SUM+[BX]. The content at physical

- address and the content of AX are interchanged.

# Arithmetic Instructions: ADD, ADC, INC, AAA, DAA

| Mnemonic | Meaning                     | Format  | Operation                                                  | Flags<br>affected |

|----------|-----------------------------|---------|------------------------------------------------------------|-------------------|

| ADD      | Addition                    | ADD D,S | $(S)+(D) \rightarrow (D)$<br>carry $\rightarrow$ (CF)      | ALL               |

| ADC      | Add with carry              | ADC D,S | $(S)+(D)+(CF) \rightarrow (D)$<br>carry $\rightarrow$ (CF) | ALL               |

| INC      | Increment by one            | INC D   | (D)+1 → (D)                                                | ALL but CY        |

| AAA      | ASCII adjust for addition   | AAA     | If the sum is >9,AH is incremented by 1                    | AF,CF             |

| DAA      | Decimal adjust for addition | DAA     | Adjust AL for decimal Packed BCD                           | ALL               |

# Arithmetic Instructions-SUB, SBB, DEC, AAS, DAS, NEG

| Mnemonic | Meaning                            | Format  | Operation                                                | Flags affected |

|----------|------------------------------------|---------|----------------------------------------------------------|----------------|

| SUB      | Subtract                           | SUB D,S | $(D) - (S) \rightarrow (D)$<br>Borrow $\rightarrow (CF)$ | All            |

| SBB      | Subtract<br>with<br>borrow         | SBB D,S | (D) - (S) - (CF) → (D)                                   | All            |

| DEC      | Decrement<br>by one                | DEC D   | (D) - 1 → (D)                                            | All but CF     |

| NEG      | Negate                             | NEG D   |                                                          | All            |

| DAS      | Decimal adjust for subtraction     | DAS     | Convert the result in AL to packed decimal format        | All            |

| AAS      | ASCII<br>adjust for<br>subtraction | AAS     | (AL) difference<br>(AH) dec by 1 if borrow               | CY,AC          |

# Multiplication and Division

| Mnemonic | Meaning                      | Format | Operation                                                                                                                                                                                                       | Flags Affected                      |

|----------|------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| MUL      | Multiply<br>(unsigned)       | MULS   | (AL) · (S8) → (AX)<br>(AX) · (S16) → (DX),(AX)                                                                                                                                                                  | OF, CF<br>SF, ZF, AF, PF undefined  |

| DIV      | Division<br>(unsigned)       | DIVS   | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                  | OF, SF, ZF, AF, PF, CF<br>undefined |

| ,        | 20 00                        |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is $FF_{16}$ in case (1) or<br>$FFF_{16}$ in case (2), then<br>type 0 interrupt occurs                                   |                                     |

| IMUL     | Integer multiply<br>(signed) | IMUL S | (AL) · (S8) → (AX)<br>(AX) · (S16) → (DX),(AX)                                                                                                                                                                  | OF, CF<br>SF, ZF, AF, PF undefined  |

| IDIV     | Integer divide<br>(signed)   | IDIV S | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                  | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                              |        | (2) Q((DX,AX)/(S16)) → (AX)<br>R((DX,AX)/(S16)) → (DX)<br>If Q is positive and exceeds<br>7FF <sub>16</sub> or if Q is negative<br>and becomes less than<br>8001 <sub>16</sub> , then type 0 interupt<br>occurs | R                                   |

| AAM      | Adjust AL for                | AAM    | $Q((AL)/10) \rightarrow (AH)$                                                                                                                                                                                   | SF, ZF, PF                          |

|          | multiplication               |        | $R((AL)/10) \rightarrow (AL)$                                                                                                                                                                                   | OF, AF,CF undefined                 |

| AAD      | Adjust AX for division       | AAD    | (AH) · 10 + (AL) → (AL)<br>00 → (AH)                                                                                                                                                                            | SF, ZF, PF<br>OF, AF, CF undefined  |

| CBW      | Convert byte to word         | CBW    | (MSB of AL) → (All bits of AH)                                                                                                                                                                                  | None                                |

| CMD      | Convert word to double word  | CWD    | (MSB of AX) → (All bits of DX)                                                                                                                                                                                  | None                                |

(a)

Reg8 Reg16 Mem8 Mem16

(b)

# Multiplication and Division

| Multiplication<br>(MUL or IMUL) | Multiplicand | Operand<br>(Multiplier) | Result   |

|---------------------------------|--------------|-------------------------|----------|

| Byte*Byte                       | AL           | Register or memory      | AX       |

| Word*Word                       | AX           | Register or memory      | DX :AX   |

| Dword*Dword                     | EAX          | Register or memory      | EAX :EDX |

| Division<br>(DIV or IDIV) | Dividend | Operand<br>(Divisor) | Quotient: Remainder |

|---------------------------|----------|----------------------|---------------------|

| Word/Byte                 | AX       | Register or Memory   | AL : AH             |

| Dword/Word                | DX:AX    | Register or Memory   | AX : DX             |

| Qword/Dword               | EDX: EAX | Register or Memory   | EAX : EDX           |

#### **AND** instruction

- This instruction logically ANDs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location.

- The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined.

- General Format:

- AND Destination, Source

#### **Example:**

- AND BL, AL ;suppose BL=1000 0110 and AL = 1100 1010 then after the operation BL would be BL= 1000 0010.

- AND CX, AX ;CX <= CX AND AX</li>

- AND CL, 08 ;CL<= CL AND (0000 1000)

#### **OR** instruction

- This instruction logically ORs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location.

- The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined.

- General Format:

- OR Destination, Source

#### **Example:**

- OR BL, AL; suppose BL=1000 0110 and AL = 1100 1010 then after the operation BL would be BL= 1100 1110.

- OR CX, AX;CX <= CX AND AX</li>

- OR CL, 08;CL<= CL AND (0000 1000)</li>

#### **NOT** instruction

The NOT instruction complements (inverts) the contents of an operand register or a memory location, bit by bit. The examples are as follows:

#### **Example:**

- NOT AX (BEFORE AX= (1011)2= (B) 16 AFTER EXECUTION AX= (0100)2= (4)16).

- NOT [5000H]

#### **XOR** instruction

• The XOR operation is again carried out in a similar way to the AND and OR operation. The constraints on the operands are also similar. The XOR operation gives a high output, when the 2 input bits are dissimilar. Otherwise, the output is zero. The example instructions are as follows:

### **Example:**

- XOR AX,0098H

- XOR AX,BX

- XOR AX,[5000H]

#### **Shift / Rotate Instructions**

- Shift instructions move the binary data to the left or right by them within the shifting register or memory location. They also can multiplication of powers of 2+n and perform division of powers of 2-n.

- There are two type of shifts logical shifting and arithmetic shifting,

later is used with signed numbers while former with unsigned.

### \$HL/SAL instruction

- Both the instruction shifts each bit to left, and places the MSB in CF and LSB is made 0. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- All flags are affected.

#### **General Format:**

SAL/SHL destination, count

#### **SHR** instruction

- This instruction shifts each bit in the specified destination to the

O is stored in the MSB position. The LSB is shifted into the carry flag. The destination can be of byte size

or of word size, also it can be a register or a memory location. Number of shifts is indicated by the

count.

- All flags are affected

- General Format:

SHR destination, count

# String Instruction Basics

**String** - a byte or word array located in memory.

**Operations** that can be performed with string instructions:

- copy a string into another string

- search a string for a particular byte or word

- store characters in a string

- compare strings of characters alphanumerically

# String Instruction Basics

- Source DS:SI, Destination ES:DI

- You must ensure DS and ES are correct

- You must ensure SI and DI are offsets into DS and ES respectively

- Direction Flag (0 = Up, 1 = Down)

- CLD Increment addresses (left to right)

- STD Decrement addresses (right to left)

# String Control Instructions

1) MOVS/ MOVSB/ MOVSW

Dest string name, src string name

This instruction moves data byte or word from location in DS to location in ES.

- 2) REP / REPZ / REPNE / REPNZ Repeat string instructions until specified conditions exist. This is prefix a instruction.

- 3) CMPS / CMPSB / CMPSW

Compare string bytes or string words.

# String Control Instructions

4)SCAS / SCASB / SCASW

Scan a string byte or string word.

Compares byte in AL or word in AX. String address is to be loaded in DI.

5) STOS / STOSB / STOSW

Store byte or word in a string.

Copies a byte or word in AL or AX to memory location pointed by DI.

6) LODS / LODSB /LODSW

Load a byte or word in AL or AX

Copies byte or word from memory location pointed by SI into AL or AX register.

These instructions are similar to branching or looping instructions. These instructions include unconditional jump or loop instructions.

#### Classification:

- Unconditional transfer instructions

- Conditional transfer instructions

- Iteration control instructions

- Interrupt instructions

#### **Unconditional transfer instructions**

- > CALL: Call a procedure, save return address on stack

- > RET: Return from procedure to the main program.

- > JMP: Goto specified address to get next instruction

CALL instruction: The CALL instruction is used to transfer execution of program to a

subprogram or procedure.

#### **CALL** instruction

- ➤ Near call

- 1. Direct Near CALL: The destination address is specified in the instruction itself.

- 2. Indirect Near CALL: The destination address is specified in any

16-bit register, except IP.

- > Far call

- 1. Direct Far CALL: The destination address is specified in the instruction itself. It will be in different Code Segment.

- 2. Indirect Far CALL: The destination address is specified in two word memory locations pointed by a register.

#### **JMP** instruction

The processor jumps to the specified location rather than the instruction after the JMP instruction.

- Intra segment jump

- Inter segment jump

#### **RET**

RET instruction will return execution from a procedure to the next instruction after the CALL instruction in the calling program.

#### **Conditional TransferInstructions**

- **JA/JNBE**: Jump if above / jump if not below or equal

- JAE/JNB: Jump if above /jump if not below

- **JBE/JNA**: Jump if below or equal/ Jump if not above

- **JC**: jump if carry flag CF=1

- JE/JZ: jump if equal/jump if zero flag ZF=1

- **JG/JNLE**: Jump if greater/ jump if not less than or equal.

#### **Conditional Transfer Instructions**

- **JGE/JNL**: jump if greater than or equal/jump if not less than

- JL/JNGE: jump if less than/jump if not greater than or equal

- **JLE/JNG**: jump if less than or equal/ jump if not greater than

- **JNC**: jump if no carry (CF=0).

- **JNE/JNZ**: jump if not equal/ jump if not zero(ZF=0)

#### **Conditional Transfer Instructions**

- JNO: jump if no overflow(OF=0)

- **JNP/JPO**: jump if not parity/ jump if parity odd(PF=0)

- **JNS**: jump if not sign(SF=0)

- **JO**: jump if overflow flag(OF=1)

- **JP/JPE**: jump if parity/jump if parity even(PF=1)

- **JS**: jump if sign(SF=1).

#### **Iteration Control Instructions**

- These instructions are used to execute a series of instructions for certain number of times.

- > LOOP: Loop through a sequence of instructions until CX=0.

- ➤ LOOPE/LOOPZ: Loop through a sequence of instructions while ZF=1 and instructions CX = 0.

- ➤ **LOOPNE/LOOPNZ**: Loop through a sequence of instructions while ZF=0 and CX =0.

- > JCXZ: jump to specified address if CX=0.

## Interrupt Instructions

#### Two types of interrupt instructions:

- ➤ Hardware Interrupts (External Interrupts)

- Software Interrupts (Internal Interrupts and Instructions)

#### **Hardware Interrupts:**

- INTR is a maskable hardware interrupt.

- NMI is a non-maskable interrupt.

## Interrupt Instructions

#### **Software Interrupts**

- INT : Interrupt program execution, call service procedure

- INTO: Interrupt program execution if OF=1

- IRET: Return from interrupt service procedure to main program.

## High Level Language Interface Instructions

> ENTER : enter procedure.

➤ LEAVE: Leave procedure.

➤ BOUND: Check if effective address within specified array bounds.

#### Processor Control Instructions

- I. Flag set/clear instructions

- > STC: Set carry flag CF to 1

- CLC: Clear carry flag CF to 0

- CMC: Complement the state of the carry flag CF

- > STD: Set direction flag DF to 1 (decrement string pointers)

- CLD: Clear direction flag DF to 0

- STI: Set interrupt enable flag to 1(enable INTR input)

- CLI: Clear interrupt enable Flag to 0 (disable INTR input)

#### **Processor Control Instructions**

#### II. External Hardware synchronizationinstructions

- ➤ HLT: Halt (do nothing) until interrupt or reset.

- ➤ WAIT: Wait (Do nothing) until signal on the test pin islow.

- ➤ ESC: Escape to external coprocessor such as 8087 or 8089.

- ➤ LOCK: An instruction prefix. Prevents another processor from taking

- the bus while the adjacent instruction executes.

- NOP: No operation. This instruction simply takes up three clock cycles and does no

processing.

- > ASSUME

- > DB

- > DD

- > DQ

- > DT

- > DW

Defined Byte. Defined

Double Word Defined Quad

Word Define Ten Bytes

Define Word

#### > ASSUME Directive-

The ASSUME directive is used to tell the assembler that the name of the logical segment should be used for a specified segment. The 8086 works directly with only 4 physical segments: a Code segment, a data segment, a stack segment, and an extra segment.

#### **Example:**

**ASUME CS:CODE**; This tells the assembler that the logical segment named CODE contains the instruction statements for the program and should be treated as a code segment.

**ASSUME DS:DATA**; This tells the assembler that for any instruction which refers to a data in the data segment, data will found in the logical segment DATA.

➤ **DB** - DB directive is used to declare a byte-type variable or to in memory location.

store a byte

#### **Example:**

1. PRICE DB 49h, 98h, 29h; Declare an array of 3 bytes,

named as

- PRICE and initialize.

- **2. NAME DB 'ABCDEF'**; Declare an array of 6 bytes and initialize with ASCII code for letters

- **3. TEMP DB 100 DUP(?)** ;Set 100 bytes of storage in memory and give it the name as TEMP, but leave the 100 bytes uninitialized. Program instructions will load values into these locations.

- The DW directive is used to define a variable of type word or to reserve storage location of type word in memory.

- **Example:**

- MULTIPLIER DW 437Ah; this declares a variable of type word and named it as MULTIPLIER. This variable is initialized with the value 437Ah when it is loaded into memory to run.

- ➤ END END directive is placed after the last statement of a program to tell the assembler that this is the end of the program module. The assembler will ignore any statement after an END directive.

- ➤ ENDP ENDPdirective is used along with the name of the procedure to indicate the end of a procedure to the assembler

#### **Example:**

- SQUARE\_NUM PROCE; It start the procedure, Some steps to find the square root of a number

- **SQUARE\_NUM ENDP**; Hear it is the End for the procedure

- > END

- > ENDP

- > ENDS

- > EQU

- > EVEN

- > EXTRN

- End Program

- End Procedure

- End Segment

- Equate

- Align on Even Memory Address

> ENDS - This ENDS directive is used with name of the segment to indicate the end of that logic segment.

**Example**: CODE SEGMENT ;Hear it Start the logic segment containing code;

- > CODE ENDS ; End of segment named as CODE

- ➤ **GLOBAL** Can be used in place of a PUBLIC directive or in place of an EXTRN directive.

- ➤ **GROUP** Used to tell the assembler to group the logical statements named after the directive into one logical group segment, allowing the contents of all the segments to be accessed from the same group segment base.

- From the named file into the current source module.

- ➤ LABEL- Used to give a name to the current value in the location counter.

- ➤ NAME- Used to give a specific name to each assembly module when programs consisting of several modules are written.

➤ **OFFSET-** Used to determine the offset or displacement of a named item or procedure from the start of the segment which contains it.

E.g.: MOV BX, OFFSET PRICES

➤ **ORG-** The location counter is set to 0000 when the assembler starts reading a segment. The ORG directive allows setting a desired value at any point in the program.

data

E.g.: ORG 2000H

**PUBLIC-** Used to tell the assembler that a specified name or label accessed from other modules.

will be

**SEGMENT-** Used to indicate the start of a logical segment.

E.g.: CODE SEGMENT indicates to the assembler the start of a segment called CODE

logical

**SHORT-** Used to tell the assembler that only a 1 byte displacement is needed to code a jump instruction.

E.g.: JMP SHORT NEARBY\_LABEL

> TYPE - Used to tell the assembler to determine the type of specified variable.

# Write an assembly language program for addition of two 8- bit numbers using 8086 microprocessors.

50H A2 DB 51H RES

DATA ENDS

**CODE SEGMENT**

ASSUME CS: CODE, DS:DATA

START: MOV AX, DATA MOV

DS,AX MOV AL,A1

MOV BL, A2 ADD AL, BL

MOV RES,AL MOV

AX,4C00H INT 21H

**CODE ENDS**

**END START**

Write an assembly language program to find the factorial of given number using 8086 microprocessors.

```

DATA SEGMENT

FIRST DW 03H

SEC DW 01H

DATA ENDS

CODE SEGMENT

ASSUME CS:CODE, DS:DATA

MOV AX, DATA MOV

START:

DS,AX MOV AX,SEC

MOV CX,FIRST

L1: MUL CX

DEC CX

JCXZ L2 JMP L1

L2: INT 3H

CODE ENDS

END START

```

## Write an assembly language program to find the sum of squares using 8086 microprocessors.

```

DATA SEGMENT

NUM DW 5H

RES DW?

DATA ENDS

CODE SEGMENT

ASSUME CS: CODE, DS: DATA

MOV AX, DATA MOV

START:

DS,AX MOV CX,NUM

MOV BX,00

MOV AX,CX MUL

L1:

CX ADD BX,AX

DEC CX

JNZ L1

MOV RES, BX INT

3H

```

CODE ENDS END START

#### **Procedures:**

While writing programs, it may be the case that a particular sequence of instructions is used several

times. To avoid writing the sequence of instructions again and again in the program, the same sequence

can be written as a separate subprogram called a procedure.

#### **Defining Procedures:**

Assembler provides PROC and ENDP directives in order to define procedures. The directive PROC indicates beginning of a procedure. Its general form is: Procedure\_name PROC [NEAR|FAR]

#### Passing parameters to and from procedures:

The data values or addresses passed between procedures and main program are called parameters. There are four ways of passing parameters:

- Passing parameters in registers

- Passing parameters in dedicated memory locations

- Passing parameters with pointers passed in registers

- Passing parameters using the stack

#### **MACROS:**

When the repeated group of instruction is too short or not suitable to be implemented as a procedure, we use a MACRO. A macro is a group of instructions to which a name is given. Each time a macro is called in a program, the assembler will replace the macro name with the group of instructions.

#### **Defining MACROS:**

Before using macros, we have to define them. MACRO directive informs the assembler the beginning of a macro. The general form is:

Macro\_name MACRO argument1, argument2, ... Arguments are optional. ENDM informs the

assembler the end of the macro. Its general form is: ENDM

| Procedures                                                                        | Macros                                                                         |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Accessed by CALL and RET mechanism                                                | Accessed by name given to macro                                                |

| during program execution                                                          | when defined during assembly                                                   |

| Machine code for instructions only put in memory once                             | Machine code generated for instructions each time called                       |

| Parameters are passed in registers,<br>memory locations or stack                  | Parameters passed as part of statement which calls macro                       |

| Procedures uses stack                                                             | Macro does not utilize stack                                                   |

| A procedure can be defined anywhere in program using the directives PROC and ENDP | A macro can be defined anywhere in program using the directives MACRO and ENDM |

| Procedures takes huge memory for CALL(3 bytes each time CALL is used) instruction | Length of code is very huge if macro's are called for more number of times     |

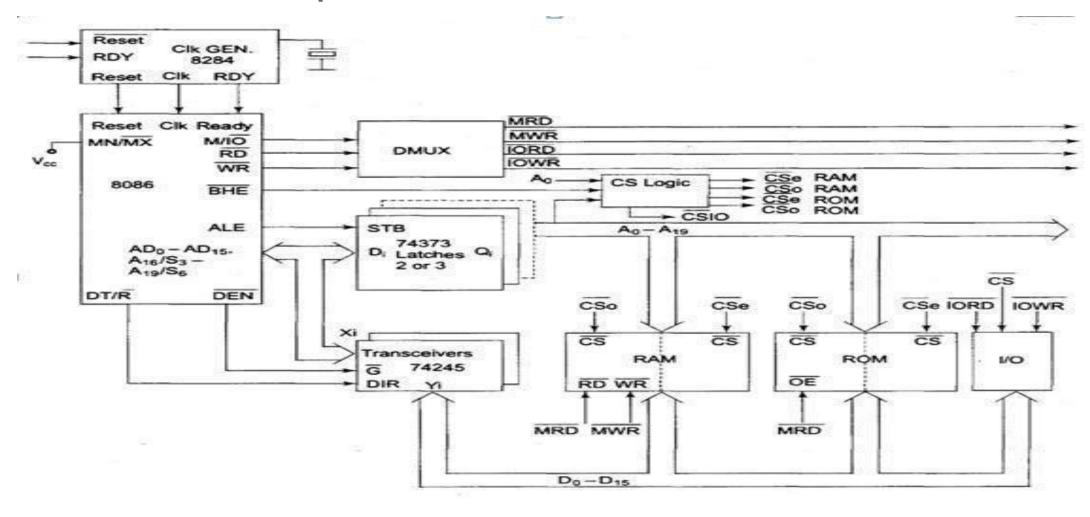

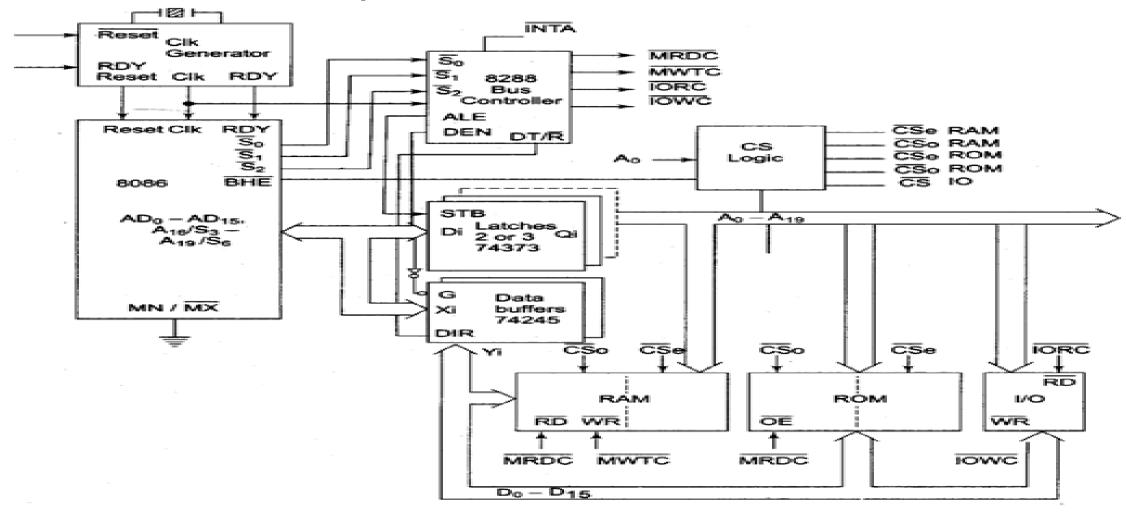

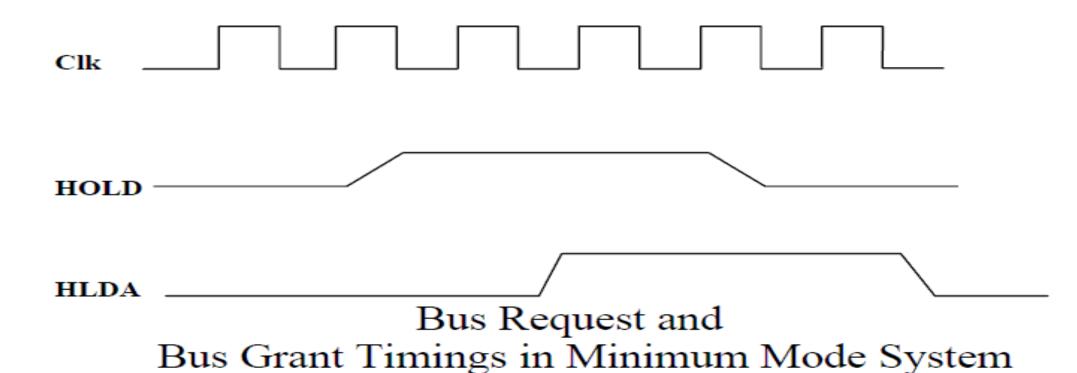

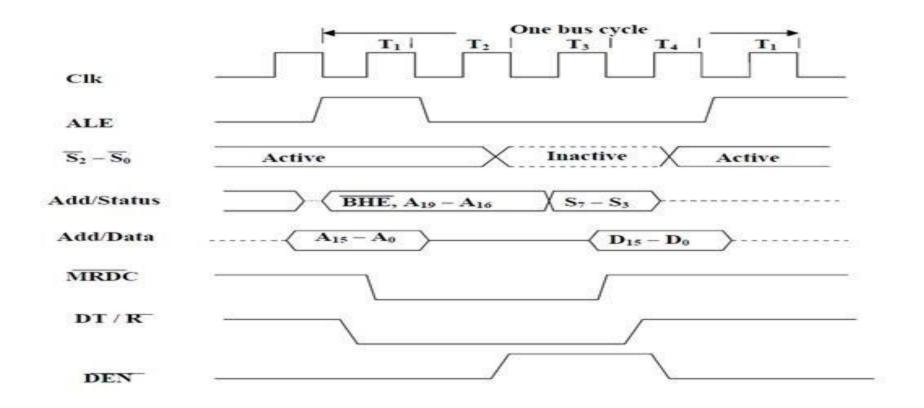

- In a minimum mode 8086 system, the microprocessor 8086 is operated in minimum mode by strapping its MN/MX pin to logic 1.

- In this mode, all the control signals are given out by the microprocessor chip itself. There is a single microprocessor in the minimum mode system.

- The remaining components in the system are latches, transceivers, clock generator, memory and I/O devices. Some type of chip selection logic may be required for selecting memory or I/O devices, depending upon the address map of the system.

- ➤ Latches are generally buffered output D-type flip-flops like 74LS373 or 8282. They are used for separating the valid address from the multiplexed address/data signals and are controlled by the ALE signal generated by 8086.

Transceivers are the bidirectional buffers and sometimes they are called as data amplifiers. They are required to separate the valid data from the time multiplexed address/data signals.

They are controlled by two signals namely, DEN and DT/R.

The DEN signal indicates the direction of data, i.e. from or to the processor. The system contains memory for the monitor and users program storage.

Usually, EPROM is used for monitor storage, while RAM for users program storage. A system may contain I/O devices.

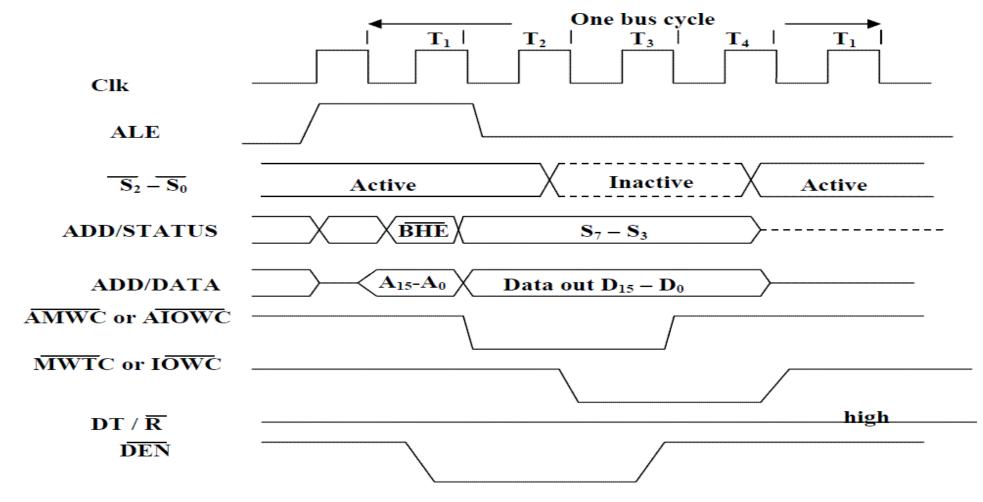

In the maximum mode, the 8086 is operated by strapping the MN/MX pin to ground.

In this mode, the processor derives the status signal S2, S1, S0. Another chip called bus controller derives the control signal using this status information.

In the maximum mode, there may be more than one

microprocessor in the system configuration.

The components in the system are same as in the minimum mode system.

The basic function of the bus controller chip IC8288 is to derive

control

signals like RD and WR (for memory and I/O devices), DEN, DT/R, ALE etc. using the information by the processor on the status lines.

The bus controller chip has input lines S2, S1, S0 and CLK. These inputs to 8288 are driven by CPU.

- It derives the outputs ALE, DEN, DT/R, MRDC, MWTC, AMWC, IORC, and AIOWC. The AEN, IOB and CEN pins are especially useful for multiprocessor systems.

- AEN and IOB are generally grounded. CEN pin is usually tied to +5V. The significance of the MCE/PDEN output depends upon the status of the IOB pin.

**IOWC**

If IOB is grounded, it acts as master cascade enable to control cascade 8259A, else it acts as peripheral data enable used in the multiple bus configurations.

- INTA pin used to issue two interrupt acknowledge pulses to the interrupt controller or to an interrupting device.

- IORC, IOWC are I/O read command and I/O write command signals respectively.

- These signals enable an IO interface to read or write the data from or to the address port.

- The MRDC, MWTC are memory read command and memory write command signals respectively and may be used as memory read or write signals.

The MRDC, MWTC are memory read command and memory write command signals respectively and may be used as memory read or signals.

write

All these command signals instructs the memory to accept or send from or to the bus. data

- For both of these write command signals, the advanced signals namely AIOWC and AMWTC are available.

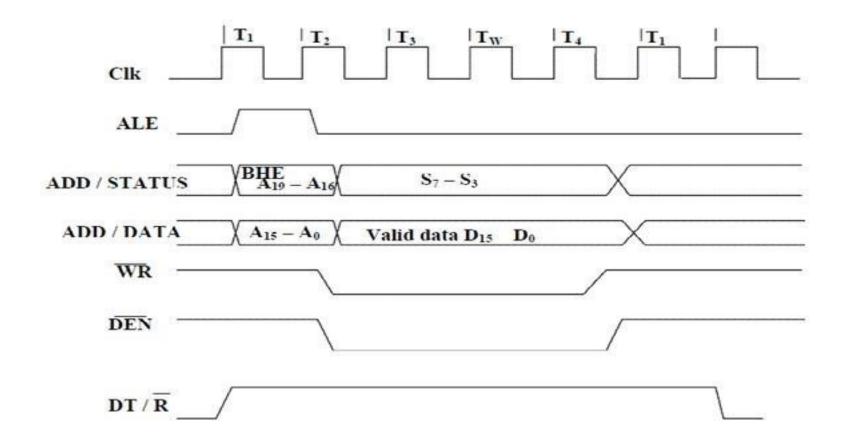

- Here the only difference between in timing diagram between minimum mode and maximum mode is the status signals used and the available control and advanced command signals.

R0, S1, S2 are set at the beginning of bus cycle.8288 bus controller will output a pulse as on the ALE and apply a required signal to its DT / R pin during T1.

In T2, 8288 will set DEN=1 thus enabling transceivers, and for an input it will activate MRDC or IORC. These signals are activated until T4. For an output, the AMWC or AIOWC is activated from T2 to T4 and

MWTC or IOWC is activated from T3 to T4.

#### Write Cycle Timing Diagram for Minimum Mode

### Memory Read Timing Diagram in Maximum Mode of 8086

# Memory Write Timing in Maximum mode of 8086

# Assembly Language Programming

The assembly programming language is a low-level language which is using mnemonics. developed by The microcontroller or microprocessor can understand only the binary language like 0's or 1's therefore the assembler convert the assembly language to binary language and store it the memory to perform the tasks. Before writing the program the embedded designers must have sufficient knowledge on particular hardware of the controller or processor, so first we required to know hardware of 8086 processor.

#### **Machine Language:**

Set of fundamental instructions the machine can execute Expressed as a pattern of 1's and 0's

### Assembly Language Programming

#### **Assembly Language:**

Alphanumeric equivalent of machine language Mnemonics more humanoriented than 1's and 0's

#### **Assembler:**

Computer program that transliterates (one-to-one mapping) assembly to machine language

Computer's native language is machine/assembly language

### Why Assembly Language Programming

- Faster and shorter programs: Compilers do not always generate optimum code.

- Instruction set knowledge is important for machine designers.

- Compiler writers must be familiar with details of machine language.

- Small controllers embedded in many products

- Have specialized functions,

- Rely so heavily on input/output functionality,

- HLLs inappropriate for product development.

### Basic Elements of 8086 Assembly Programming Language

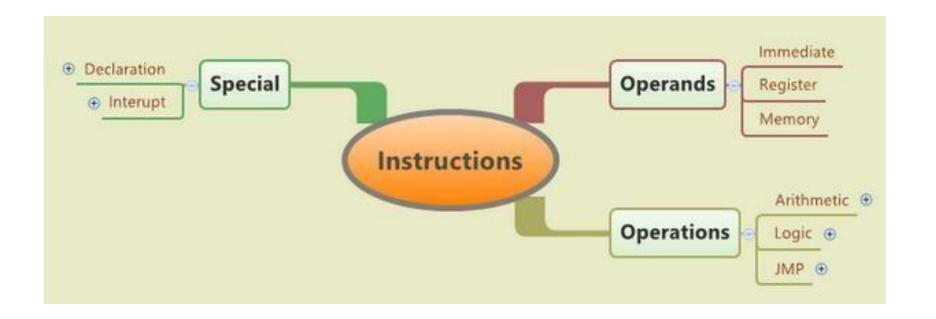

# 8086 Assembly Programming Language Instructions

• Like we know instruction are the lines of a program that means an action for the computer to execute.

In 8086, a normal instruction is made by an operation code and sometimes operands.

#### Structure:

Operation Code [Operand1 [, Operand2]]

- Operations

- The operation is usually logic or arithmetic, but we can also find some special operation like the Jump (JMP) operation.

## 8086 Assembly Programming Language Instructions

#### Operands

- Operands are the parameters of the operation in the instruction. They can be use in 3 way:

- Immediate

- This means a direct access of a variable that have been declared in the program.

- Register

- Here we use the content of a register to be a parameter.

- Memory

- Here we access to the content of a specific part of the memory using a pointer

### SYNTAX OF 8086/8088 ASSEMBLY LANGUAGE

- The language is not case sensitive.

- There may be only one statement per line. A statement may start in any column.

- A statement is either an instruction, which the assembler translates into machine code, or an assembler directive (pseudo-op), which instructs the assembler to perform some specific task.

- Syntax of a statement:

```

{name} mnemonic {operand(s)} {; comment}

```

The curly brackets indicate those items that are not present or are optional in some statements.

### SYNTAX OF 8086/8088 ASSEMBLY LANGUAGE

- The name field is used for instruction labels, procedure names, segment names, macro names, names of variables, and names of constants.

- MASM 6.1 accepts identifier names up to 247 characters long. All characters are significant, whereas under MASM 5.1, names are significant to 31 characters only. Names may consist of letters, digits, and the following 6 special characters: ? . @ \_ \$ % . If a period is used; it must be the first character. Names may not begin with a digit.

- Instruction mnemonics, directive mnemonics, register names, operator names and other words are reserved.

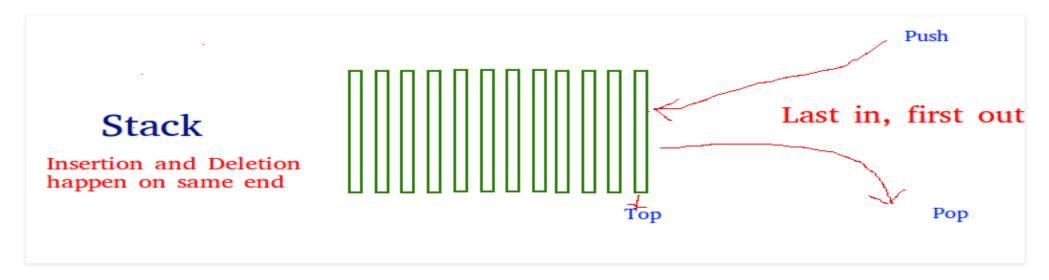

### Stack

A stack is a container of objects that are inserted and removed according to the last-in first-out (LIFO) principle. In the pushdown stacks only two operations are allowed: push the item into the stack, and pop the item out of the stack.

A stack is a container of objects that are inserted and removed according to the last-in first-out (LIFO) principle. In the pushdown stacks only two operations are allowed: push the item into the stack, and pop the item out of the stack. A stack is a limited access data structure - elements can be added and removed from the stack only at the top. push adds an item to the top of the stack, pop removes the item from the top.

### Stack

A helpful analogy is to think of a stack of books; you can remove only the top book, also you can add a new book on the top. A stack is a recursive data structure. Here is a structural definition of a Stack:

A stack is either empty or it consists of a top and the rest which is a stack;

### **Applications**

- The simplest application of a stack is to reverse a word. You push a given word to stack letter by letter and then pop letters from the stack.

- Another application is an "undo" mechanism in text editors; this operation is accomplished by keeping all text changes in a stack.

- Backtracking. This is a process when you need to access the most recent data element in a series of elements. Think of a labyrinth or maze how do you find a way from an entrance to an exit? Once you reach a dead end, you must backtrack. But backtrack to where? to the previous choice point. Therefore, at each choice point you store on a stack all possible choices. Then backtracking simply means popping a next choice from the stack.

### Stack Data Structure

Stack is a linear data structure which follows a particular order in which the operations are performed.

The order may be LIFO(Last In First Out) or FILO(First In Last Out).

Mainly the following three basic operations are performed in the stack:

- Push: Adds an item in the stack. If the stack is full, then it is said to be an Overflow condition.

- **Pop:** Removes an item from the stack. The items are popped in the reversed order in which they are pushed. If the stack is empty, then it is said to be an Underflow condition.

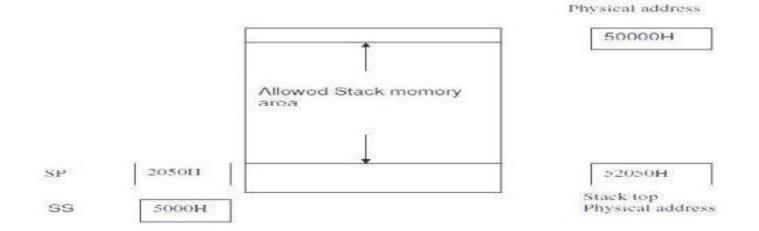

### Stack Structure

### Stack Structure

- If the stack top points to a memory location 52050H, it means that the location 52050H is already occupied with the previously pushed data. The next 16 bit push operation will decrement the stack pointer by two, so that it will point to the new stack-top 5204EH and the decremented contents of SP will be 204EH. This location will now be occupied by the recently pushed data.

- Thus for a selected value of SS, the maximum value of SP=FFFFH and the segment can have maximum of 64K locations. If the SP starts with an initial value of FFFFH, it will be decremented by two whenever a 16-bit data is pushed onto the stack.

### Stack Structure

- After successive push operations, when the stack pointer contains 0000H, any attempt to further

push the data to the stack will result in stack overflow.

- After a procedure is called using the CALL instruction, the IP is incremented to the next instruction.

Then the contents of IP, CS and flag register are pushed automatically to the stack. The control is then

transferred to the specified address in the CALL instruction i.e. starting address of the procedure.

Then the procedure is executed.

### Interrupts

#### **Definition:**

The meaning of 'interrupts' is to break the sequence of operation. While the CPU is executing a program, on 'interrupt' breaks the normal sequence of execution of instructions, diverts its execution to some other program called Interrupt Service Routine (ISR). After executing ISR, the control is transferred back again to the main program. Interrupt processing is an alternative to polling.

### Interrupts

#### **Need for Interrupt:**

Interrupts are particularly useful when interfacing I/O devices that provide or require data at relatively low data transfer rate.

Interrupt is a mechanism that allows hardware or software to suspend normal execution on microprocessor in order to switch to interrupt service routine for hardware / software. Interrupt can also describe as asynchronous electrical signal that sent to a microprocessor in order to stop current execution and switch to the execution signaled (depends on priority). Whether an interrupt is prioritized or not depends on the interrupt flag register which controlled by priority / programmable interrupt

## Interrupt Cycle of 8086

- Interrupts in 8086 microprocessor. ... Whenever an interrupt occurs the processor completes the execution of the current instruction and starts the execution of an Interrupt Service Routine (ISR) or Interrupt Handler. ISR is a program that tells the processor what to do when the interrupt occurs.

- In 8086 microprocessor following tasks are performed when microprocessor encounters an interrupt:

- The value of flag register is pushed into the stack. It means that first the value of SP (Stack Pointer) is decremented by 2 then the value of flag register is pushed to the memory address of stack segment.

### Interrupt Cycle of 8086

- The value of starting memory address of CS (Code Segment) is pushed into the stack.

- The value of IP (Instruction Pointer) is pushed into the stack.

- IP is loaded from word location (Interrupt type) \* 04.

- CS is loaded from the next word location.

- Interrupt and Trap flag are reset to 0.

# Hardware Interrupts

Hardware interrupts are those interrupts which are caused by any peripheral device by sending a signal through a specified pin to the microprocessor. There are two hardware interrupts in 8086 microprocessor.

They are: (A) NMI (Non Maskable Interrupt) – It is a single pin non maskable hardware interrupt which cannot be disabled. It is the highest priority interrupt in 8086 microprocessor. After its execution, this interrupt generates a TYPE 2 interrupt. IP is loaded from word location 00008 H and CS is loaded from the word location 0000A H.

# Hardware Interrupts

(B) INTR (Interrupt Request) – It provides a single interrupt request and is activated by I/O port. This interrupt can be masked or delayed. It is a level triggered interrupt. It can receive any interrupt type, so the value of IP and CS will change on the interrupt type received.

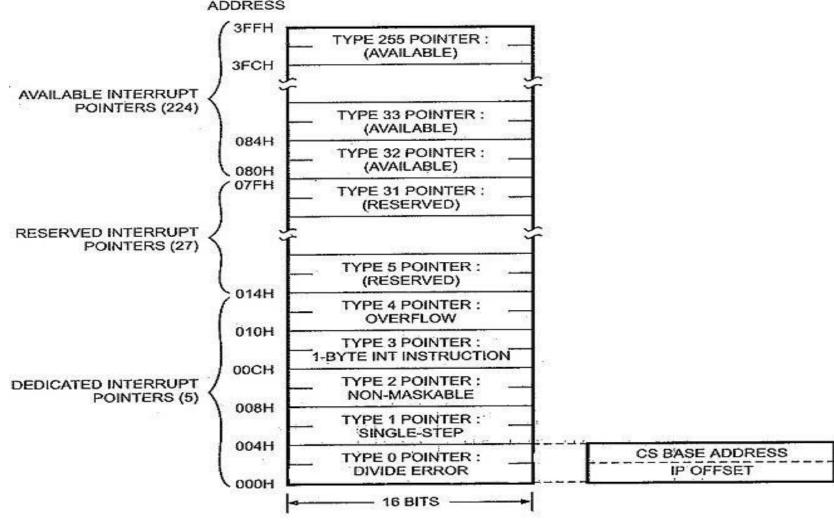

### Software Interrupts

> These are instructions that are inserted within interrupts. the program to generate

- There are 256 software interrupts in 8086 microprocessor. The instructions are of the format INT type where type ranges from 00 to FF. The starting address ranges from 00000 H to 003FF H.

- ➤ These are 2 byte instructions. IP is loaded from type \* 04 H and CS is loaded from the next address give by (type \* 04) + 02 H. Some important software interrupts are:

### Software Interrupts

TYPE 0 corresponds to division by zero(0).

- (A) TYPE 1 is used for single step execution for debugging of program.

- (B) TYPE 2 represents NMI and is used in power failure conditions.

- (C) TYPE 3 represents a break-point interrupt.

- (D) TYPE 4 is the overflow interrupt.

# nterrupt Vector Table (IVT) on 8086

# Non Maskable Interrupt

- Hardware interrupt is caused by any peripheral device by sending a signal through a specified pin to the microprocessor. The 8086 has two hardware interrupt pins, i.e. NMI and INTR. NMI is a non- maskable interrupt and INTR is a maskable interrupt having lower priority.

- t is a single non-maskable interrupt pin (NMI) having higher priority than the maskable interrupt request pin (INTR) and it is of type 2 interrupt.

- When this interrupt is activated, these actions take place –

- Completes the current instruction that is in progress.

- Pushes the Flag register values on to the stack.

### Non Maskable Interrupt

Pushes the CS (code segment) value and IP (instruction pointer) of the return address on to the stack.

value

- IP is loaded from the contents of the word location 00008H.

- CS is loaded from the contents of the next word location 0000AH.

- Interrupt flag and trap flag are reset to 0.

## Maskable Interrupt

- The 8086 has two hardware interrupt pins, i.e. ... NMI is a non-maskable interrupt and INTR is a maskable interrupt having lower priority. One moreinterrupt pin associated is INTA called interrupt acknowledge.

- The INTR is a maskable interrupt because the microprocessor will be interrupted only if interrupts are enabled using set interrupt flag instruction. It should not be enabled using clear interrupt Flag instruction.

- The INTR interrupt is activated by an I/O port. If the interrupt is enabled and NMI is disabled, then the microprocessor first completes the current execution and sends '0' on INTA pin twice.

### Maskable Interrupt

- The first '0' means INTA informs the external device to get ready and during the second '0' the microprocessor receives the 8 bit, say X, from the programmable interrupt controller.

- These actions are taken by the microprocessor –

- First completes the current instruction.

- Activates INTA output and receives the interrupt type, say X.

- Flag register value, CS value of the return address and IP value of the return address are pushed on to the stack.

- IP value is loaded from the contents of word location X × 4

- CS is loaded from the contents of the next word location.

- Interrupt flag and trap flag is reset to 0

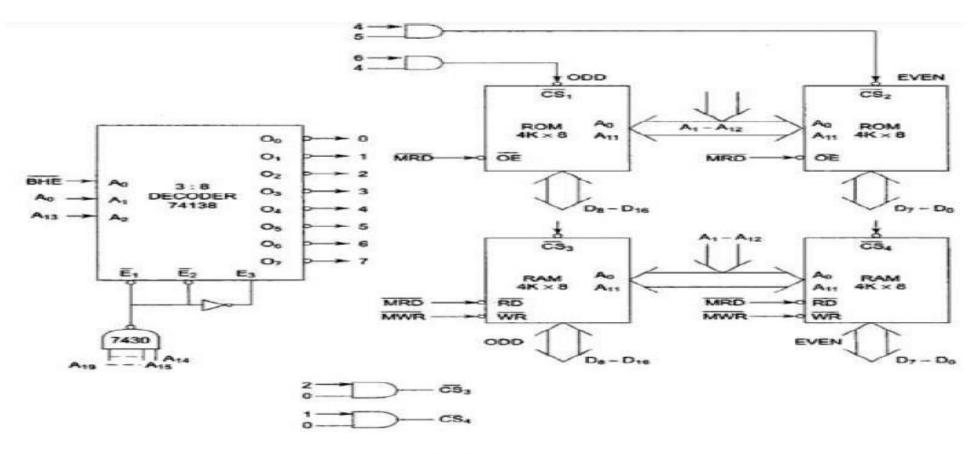

### Memory interfacing to 8086 (Static RAM and EPROM)

• Interface two 4Kx8 EPROMS and two 4Kx8 RAM chips with 8086. select suitable maps.

|         |          |      |                 |      | Table           |     | Memory Map for Problem |                 |          |                 |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |

|---------|----------|------|-----------------|------|-----------------|-----|------------------------|-----------------|----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|

| Address | A19      | A 18 | A <sub>17</sub> | A 16 | A <sub>15</sub> | A14 | A <sub>13</sub>        | A <sub>12</sub> | $A_{II}$ | A <sub>10</sub> | A <sub>09</sub> | A <sub>08</sub> | A <sub>07</sub> | A <sub>06</sub> | A <sub>05</sub> | A <sub>04</sub> | A <sub>03</sub> | A <sub>02</sub> | Aor | A <sub>00</sub> |

| FFFFFH  | 1        | 1    | 1               | 1    | 1               | 1   | 1                      | 1               | 1        | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1   | 1               |

| 調理第 176 |          |      | 271.14          | WE.  | 40.             | EPR | OM                     | -               |          |                 | F 14            | 77              | 8K×             | 8               | 300             | W.              | 11/2            | 534             | 100 | right.          |

| FE000H  | 1        | 1    | 1               | 1    | 1               | 1   | 1                      | 0               | 0        | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0   | 0               |

| FDFFFH  |          | 1    | 1               | 1    | 1               | 1   | . 0                    | 1               | 1        | 1               | 1.              | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1   | 1               |

|         | RAM 8K×8 |      |                 |      |                 |     |                        |                 |          |                 |                 |                 |                 |                 |                 |                 |                 |                 |     |                 |

| FC000H  | . 1      | 1    | 1               | 1    | 1               | 1   | 0                      | 0               | 0        | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0   | 0               |

### Memory interfacing to 8086 (Static RAM and EPROM)

Fig shows the interfacing diagram for the memory system

## Memory interfacing to 8086 (Static RAM and EPROM)

|                                 | Table      |                | Memory Ch  | ip Selec   | ion for Problem | or Problem           |  |  |

|---------------------------------|------------|----------------|------------|------------|-----------------|----------------------|--|--|

| Decoder I/P →                   |            | A <sub>2</sub> | $A_{l}$    | $A_{\phi}$ |                 | Selection/           |  |  |

| Address/BHE →                   |            | $A_{IJ}$       | $A_{\phi}$ | BHE        |                 | Comment              |  |  |

| Word transfer on $D_0 - D_{15}$ | Leeven nee | 0              | 0          | 0          | Even and        | odd addresses in RAM |  |  |

| Byte transfer on $D_7 - D_0$    |            | 0              | 0          | 1          | - Only eve      | n address in RAM     |  |  |

| Byte transfer on $D_8 - D_{15}$ |            | 0              | 1          | 0          | Only odd        | l address in RAM     |  |  |

| Word transfer on $D_0 - D_{15}$ |            | 1              | 0          | 0          | Even and        | odd addresses in ROM |  |  |

| Byte transfer on $D_0 - D_7$    |            | 1              | 0          | 1          | Only eve        | n address in ROM     |  |  |

| Byte transfer on $D_8 - D_{15}$ |            | 1              | 1. 1.      | 0          | Only odd        | l address in ROM     |  |  |

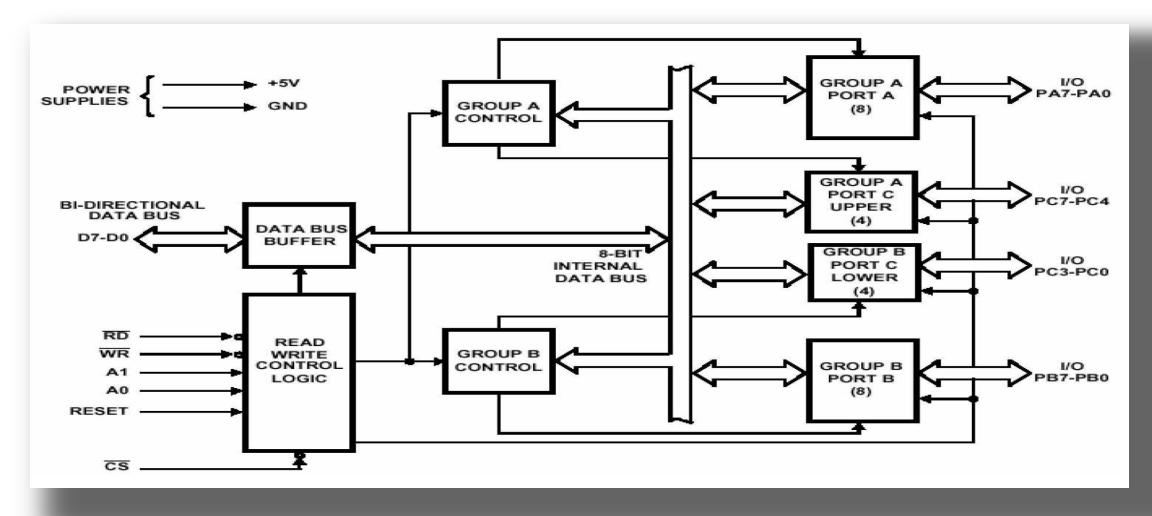

### 8255- PROGRAMMABLE PERIPHERAL INTERFACE

- ➤ It has 24 input/output lines

- ➤ 24 lines divided into 3 ports

- Port A(8bit)

- Port B(8 bit)

- Port C upper(4 bit), Port C Lower (4 bit)

All the above 3 ports can act as input or output ports

### 8255- PROGRAMMABLE PERIPHERAL INTERFACE

Figure: Block Diagram of 8255(PPI)

#### **Data Bus buffer**

> It is a 8-bit bidirectional Data bus.

Used to interface between 8255 data bus with system bus.

ightharpoonup The internal data bus and Outer pins  $D_0$ - $D_7$  pins are connected in internally.

> The direction of data buffer is decided by Read/Control Logic.

#### **Read/Write Control Logic**

This is getting the input signals from control bus and

Address Bus.

- ➤ Control signal are RD andWR.

- ➤ Address signals are A0, A1, and CS

- ➤8255 operation is enabledor disabled by CS.

Group A and B get the Control Signal from CPU and send the command to the individual control blocks.

Group A send the control signal to port A and Port C (Upper) PC7-PC4. Group B send the control signal to port B and Port C (Lower) PC3-PC0.

#### PORT A:

- This is a 8-bit buffered I/O latch.

- It can be programmed by mode 0, mode 1, mode 2.

#### **PORT B:**

- ➤ This is a 8-bit buffer I/O latch.

- ➤ It can be programmed by mode 0 and mode 1.

#### **PORTC:**

- > This is a 8-bit Unlatched buffer Input and an Output latch.

- > It is spitted into two parts.

| PA3□1    | $\sim$ | 40 PA4                |

|----------|--------|-----------------------|

| PA2□2    |        | 39 🗖 PA5              |

| PA1 □ 3  |        | 38 <mark>🗆 РА6</mark> |

| PAO 🗆 4  |        | 37 🗆 PA7              |

| RD 🗆 5   |        | 36 □ VVR              |

| ਟਤ⊏6     |        | 35 RESET              |

| GND 🗆 7  |        | 34 🗖 D0               |

| A1 ☐ 8   |        | 33 🗖 D1               |

| AO 🗆 9   |        | 32 🗖 D2               |

| PC7 🗆 10 |        | 31 🗖 D3               |

| PC6 ☐ 11 | 8255A  | 30 🗖 D4               |

| PC5 ☐ 12 |        | 29 🗆 D5               |

| PC4 ☐ 13 |        | 28 🗆 D6               |

| PC0 ☐ 14 |        | 27 🗆 D7               |

| PC1 ☐ 15 |        | 26 🗖 Vac              |

| PC2 ☐ 16 |        | 25 PB7                |

| PC3 ☐ 17 |        | 24 DPB6               |

| PB0 ☐ 18 |        | 23 PB5                |

| PB1 □ 19 |        | 22 DPB4               |

| PB2 🗆 20 |        | 21 PB3                |

|          |        |                       |

8255 Pin Diagram

Pin Description of 8255

**PA7-PA0**: These are eight port A lines that acts as either latched output or buffered input

lines depending upon the control word loaded into the control word register.

**PC7-PC4:** Upper nibble of port C lines. They may act as either output latches or input

buffers lines. This port also can be used for generation of handshake lines in

mode 1 or mode 2.

**PC3-PC0**: These are the lower port C lines, other details are the same

as PC7-PC4 lines.

**PB0-PB7**: These are the eight port B lines which are used lines or

as latched output way buffered input lines in the same

as port A.

#### Pin Description of 8255

- > RD: This is the input line driven by the microprocessor and should be low to indicate read operation to 8255.

- ➤ WR: This is an input line driven by the microprocessor. A low on this indicates writeoperation.

- >CS: This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected.

line

- >A1-A0: These are the address input lines and are driven by the microprocessor.

- > RESET: The 8255 is placed into its reset state if this input line is a

logical 1. All peripheral ports are set to the input mode.

#### Various modes of 8255:

These are two basic modes of operation of 8255. I/O mode and Bit Set-Reset mode (BSR).

#### ➤ In I/O Mode:

The 8255 ports work as programmable I/O ports, while in BSR mode only port C (PCO-PC7) can be used to set or reset its individual port bits.

Under the I/O mode of operation, further there are three modes of operation of 8255, so as to support different types of applications, mode 0, mode 1 and mode 2.

Mode 0 (Basic I/O mode): This mode is also called as basic input/output Mode. This mode provides simple input and output capabilities using each of the three ports. Data can be simply read from and written to the input and output ports respectively, after appropriate initialization.

➤ Mode 1: (Strobed input/output mode) in this mode the handshaking control the input and output action of the specified port. Port C lines PCO- PC2, provide strobe or handshake lines for port B.

- This group which includes port B and PCO-PC2 is called as group B for Strobed data input/output. Port C lines PC3-PC5 provides strobe lines for port A.

- This group including port A and PC3-PC5 from group A. Thus port C is utilized for generating handshake signals.

▶ Mode 2 (Strobed bidirectional I/O): This mode of operation of 8255 is also called as strobed bidirectional I/O. This mode of operation provides 8255 with additional features for communicating with a peripheral device on an 8-bit data bus.

Handshaking signals are provided to maintain proper synchronization data flow and between the data transmitter and receiver.

The interrupt generation and other functions are similar to mode 1.

#### > BSR Mode:

In this mode any of the 8-bits of port C can be set or reset depending on D0 of the control word. The bit

to be set or reset is selected by bit select flags D3, D2 and D1 of the CWR as given in table.

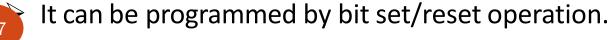

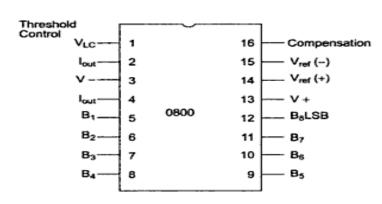

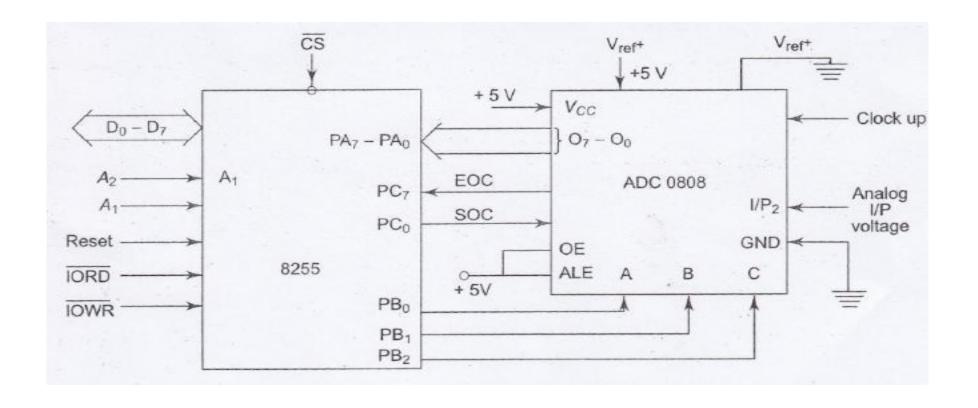

## 8255 interfacing with 8086:

8255 – 8086 Interfacing - 8 Bit Input - Output

Interfacing the 8255 PPI to the 8086 microprocessor

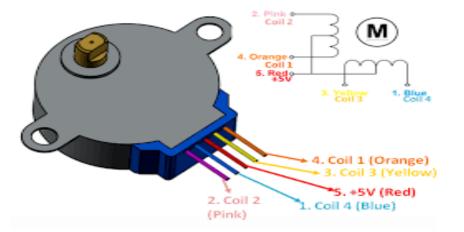

### Stepper motor

> Stepper motor is often used in computer systems. Normally DC and AC motors move smoothly in a circular fashion.

Stepper motor is a DC motor, specially designed, which moves in discrete or fixed step and thus complete one rotation of 360 degrees. To rotate the shaft of the motor a sequence of pulses are applied to the windings in a predefined sequence.

The number of pulses required to complete one rotation depends on the number of teeth on the rotor. Hence rotation Per pulse sequence is 360°/NT where NT is the number of teeth on rotor.

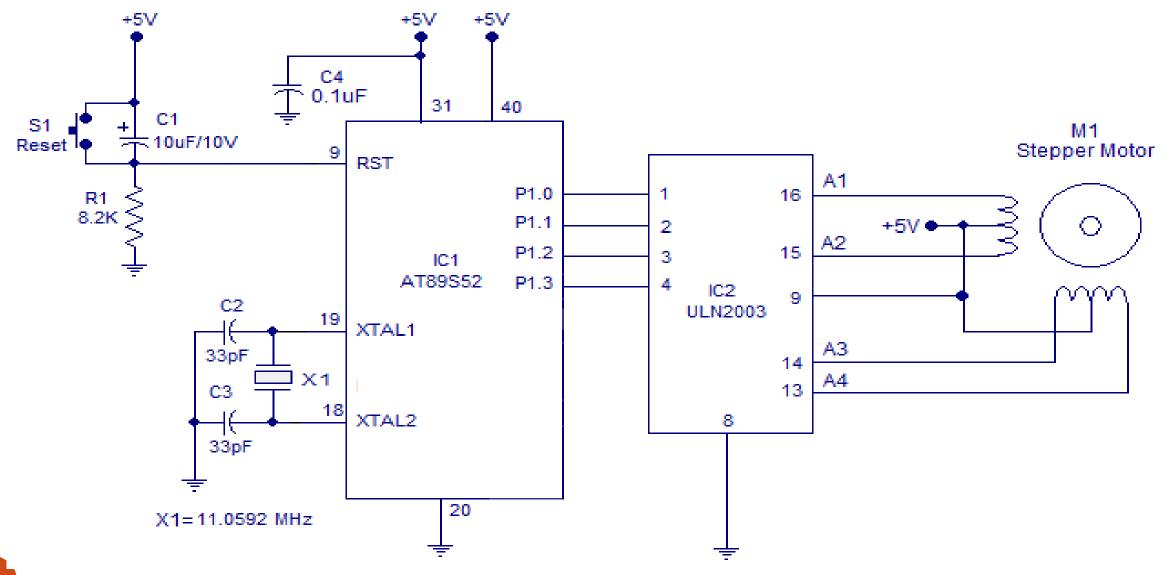

# Stepper motor Programs for Stepper Motor Rotation:

1. Program to rotate the stepper motor continuously in clockwise direction for following specification

NT = Number of teeth on rotor = 200 Speed of motor = 12

rotations/minute. CPU frequency = 10MHz

## epper motor

PORTC EQU 8004H

CNTLPRT EQU 8006H DELAY

EQU 14705

DATA ENDS

**CODE SEGMENT**

ASSUME CS: CODE, DS: DATA

START:

MOV AX, DATA MOV

DS, AX MOV AL, 80H

MOV DX, CNTLPORT OUT

DX, AL

MOV AL, 33H MOV DX,

PORTC OUT DX, AL

ROR AL, 1 MOV CX,

BACK:

DELAY LOOP SELF

**DELAY LOOP FOR 25Ms**

JMP BACK

SELF:

**CODE ENDS END START**

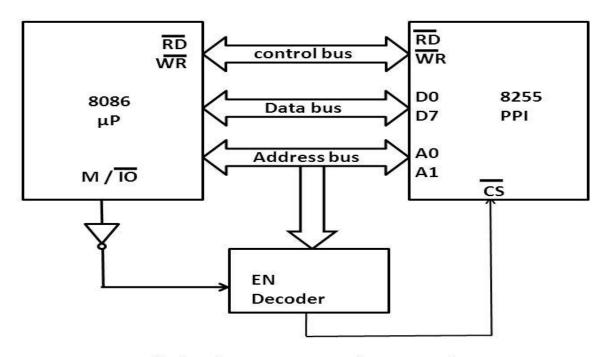

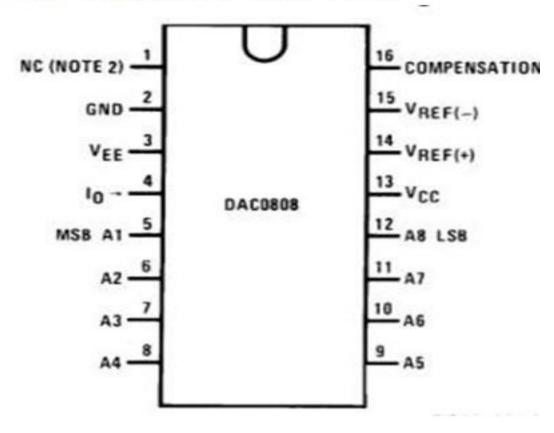

## Digital to analog converter interfacing

#### **DAC0800 8-bit Digital to Analog Converter**