# VEMU INSTITUTE OF TECHNOLOGY P.KOTHA KOTA CHITTOOR

# LINEAR AND DIGITAL IC APPLICATIONS

Prepared by:

Mrs. S.LEELALA LAKSHMI, Professor, HOD

#### Course Contents

- Unit 1 Operational Amplifier

- Unit 2 OP-Amp,IC555 & IC565 Applications

- Unit 3 / Active filters and other Ic's

- Unit 4 Voltage regulators and converts

- Unit 5 Cmos logic,Combinational circuits

Sequential Logic IC's & Memories

#### Unit 1- Integrated Circuits

- What is an Integrated Circuit?

- Where do you use an Integrated Circuit?

- Why do you prefer an Integrated Circuit to the circuits made by interconnecting discrete components?

<u>Def</u>: The "Integrated Circuit " or IC is a miniature, low cost electronic circuit consisting of active and passive components that are irreparably joined together on a single crystal chip of silicon.

#### **Applications of an Integrated Circuit**

- Communication

- Control

- Instrumentation

- Cømputer

#### Advantages

•

- Small size

- Low cost

- Less weight

- Low supply voltages

- Low power consumption

- Highly reliable

- Matched devices

- Fast speed

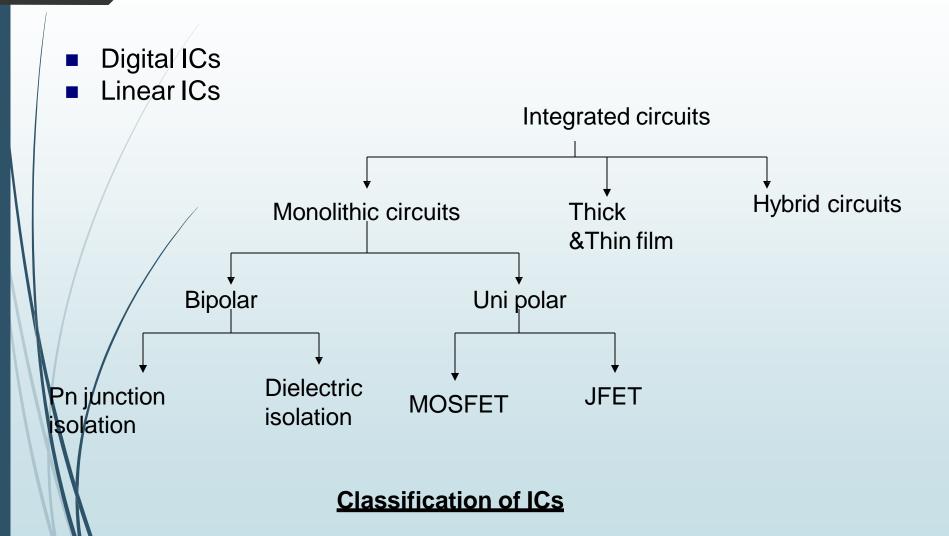

#### Classification

## Chip size and Complexity

Invention of Transistor (Ge) - 1947

■ Development of Silicon - 1955-1959

Silicon Planar Technology - 1959

■ First ICs, SSI (3-30gates/chip) - 1960

■ MSI (30-300 gates/chip) - 1965-1970

VLSI (More than 3k gates/chip) - 1975

ULSI (more than one million active devices are integrated on single chip)

| SSI          | MSI       | LSI     | VLSI        | ULSI        |

|--------------|-----------|---------|-------------|-------------|

| < 100 active | 100-1000  | 1000-   | >100000     | Over 1      |

| devices      | active    | 100000  | active      | million     |

|              | devices   | active  | devices     | active      |

|              |           | devices |             | devices     |

| Integrated   | BJT's and | MOSFETS | 8bit, 16bit | Pentium     |

| resistors,   | Enhanced  |         | Microproces | Microproces |

| diodes/&     | MOSFETS   |         | sors        | sors        |

| BJT's/       |           |         |             |             |

#### Selection of IC

| Туре                 | Package Criteria                                                                                                                               |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Metal can<br>package | <ol> <li>Heat dissipation is important</li> <li>For high power applications like power amplifiers, voltage regulators etc.</li> </ol>          |

| DIP                  | <ol> <li>For experimental or bread boarding purposes as easy to mount</li> <li>If bending or soldering of the leads is not required</li> </ol> |

|                      | 3. Suitable for printed circuit boards as lead spacing is more                                                                                 |

| Flat pack            | More reliability is required                                                                                                                   |

|                      | 2. Light in weight                                                                                                                             |

|                      | 3. Suited for airborne applications                                                                                                            |

# Factors affecting selection of IC package

- Relative cost

- Reliability

- Weight of the package

- Ease of fabrication

- Power to be dissipated

- Meed of external heat sink

#### Temperature Ranges

- 1. Military temperature range : -55° C to +125° C (-55° C to +85° C)

- 2. Industrial temperature range : -20° C to +85° C (-40° C to +85° C )

- 3. Commercial temperature range: 0°C to +70°C (0°C to +75°C)

### **Operational Amplifier**

The operational amplifier (Op-Amp) is a multiterminal device which internally is quite complex.

### Operational Amplifier

An "Operational amplifier" is a direct coupled high-gain amplifier usually consisting of one or more differential amplifiers and usually followed by a level translator and output stage.

The operational amplifier is a versatile device that can be used to amplify dc as well as ac input signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration.

### **Basic Information of Op-Amp**

Op-amps have five basic terminals, that is, two input terminals, one output terminal and two power supply terminals.

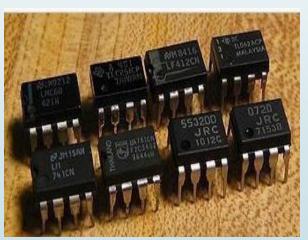

### Package s

The Dual-in-Line (DIP)

Package

The Flat Package

### Basic Information of an Op-amp contd...

Power supply connection:

The power supply voltage may range from about ± 5V to ± 22V.

The common terminal of the V+ and V- sources is connected to a reference point or ground.

### Manufacturer's Designation for Linear ICs

Fairchild

National Semiconductor

Motorola

■ RCA

Texas Instruments

Signetics

Burr- Brown

- μΑ, μΑΓ

- LM,LH,LF,TBA

- MC,MFC

- CA,CD

- SN

- N/S,NE/SE

- BB

# Fairchild's original µA741 is also manufactured by other manufactures as follows

- MC1741

- CA3741

National Semiconductor - LM741

Motorola

RCA

Texas Instruments - SN52741

Signetics - N5741

741 Military grade op-amp

■ 741C Commercial grade op-amp

741A Improved version of 741

■ 741É Improved version of 741C

741S Military grade op-amp with higher slewrate

▼ 741SC Commercial grade op-amp with higher slew rate

### Differential Amplifier

$$V_0 = A_d (V_1 - V_2)$$

$$A_d = 20 \log_{10} (A_d) \text{ in dB}$$

$$V_c = \frac{(V_1 + V_2)}{2}$$

CMRR=  $\rho = \begin{vmatrix} 2 \end{vmatrix} A$

## Characteristics and performance parameters of Op-amp

- Input offset Voltage

- Input offset current

- Input bias current

- Differential input resistance

- Input capacitance

- Open loop voltage gain

- CMRR

- Output voltage swing

# Characteristics and performance parameters of Op-

- Output resistance

- Offset adjustment range

- Input Voltage range

- Power supply rejection ratio

- Power consumption

- Slew rate

- Gain Bandwidth product

- Equivalent input noise voltage and current

### Characteristics and performance parameters of Op-

- Average temperature coefficient of offset parameters

- Output offset voltage

- Supply current

# Input Offset Voltage

The differential voltage that must be applied between the two input terminals of an op-amp, to make the output voltage zero.

It is denoted as V<sub>ios</sub>

For op-amp 741C the input offset voltage is 6mV

### 2. Input offset current

The algebraic difference between the currents flowing into the two input terminals of the op-amp

It is denoted as

$$I_{ios} = |I_{b1} - I_{b2}|$$

For op-amp 741C the input offset current is 200nA

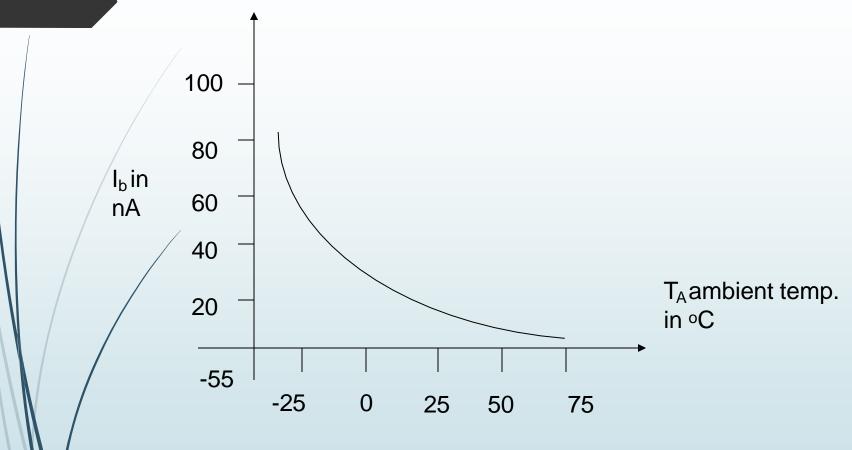

### 3. Input bias current

The average value of the two currents flowing into the op-amp input terminals

It is expressed mathematically as

$$\frac{I_{b1} + I_{b2}}{2}$$

For 741C the maximum value of I<sub>b</sub> is 500nA

### 4. Differential Input Resistance

It is the equivalent resistance measured at either the inverting or non-inverting input terminal with the other input terminal grounded

#### It is denoted as R<sub>i</sub>

For 741C it is of the order of  $2M\Omega$

#### 5. Input capacitance

It is the equivalent capacitance measured at either the inverting or non- inverting input terminal with the other input terminal grounded.

#### It is denoted as C<sub>i</sub>

For 741C it is of the 1-4 pF

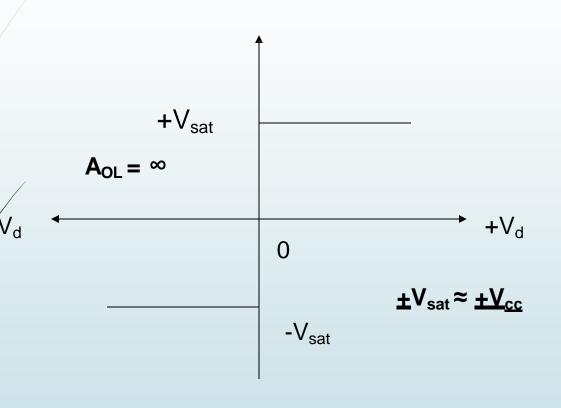

### 6. Open loop Voltage gain

It is the ratio of output voltage to the differential input voltage, when op-amp is in open loop configuration, without any feedback. It is also called as large signal

voltage gain

It is/denoted as A<sub>OL</sub>

$$A_{OL}=V_{o}/V_{d}$$

For 741C it is typically 200,000

#### 7. CMRR

It is the ratio of differential voltage gain  $A_d$  to common mode voltage gain  $A_c$

$$CMRR = A_d/A_c$$

$A_d$  is open loop voltage gain  $A_{OL}$  and  $A_c = V_{OC}/V_c$

For op-amp 741C CMRR is 90 dB

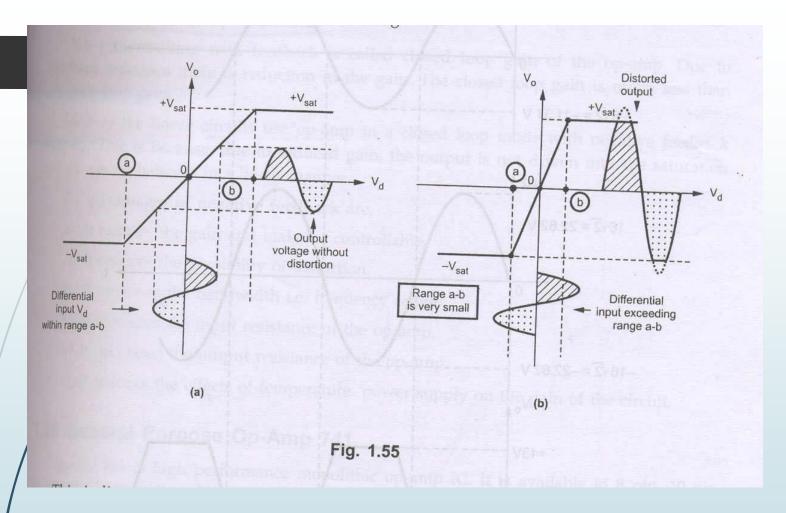

## 8. Output Voltage swing

The op-amp output voltage gets saturated at  $+V_{cc}$  and  $-V_{EE}$  and it cannot produce output voltage more than  $+V_{cc}$  and  $-V_{EE}$ . Practically voltages  $+V_{sat}$  and  $-V_{sat}$  are slightly less than  $+V_{cc}$  and  $-V_{EE}$ .

For op-amp 741C the saturation voltages are ± 13V for supply voltages ± 15V

### 9. Output Resistance

It is the equivalent resistance measured between the output terminal of the op-amp and ground

It is denoted as R<sub>o</sub>

For op-amp 741 it is  $75\Omega$

# 10. Offset voltage adjustment range

The range for which input offset voltage can be adjusted using the potentiometer so as to reduce output to zero

For op-amp 741C it is ± 15mV

### 11. Input Voltage range

It is the range of common mode voltages which can be applied for which op-amp functions properly and given offset specifications apply for the op-amp

For  $\pm$  15V supply voltages, the input voltage range is  $\pm$  13V

### 12. Power supply rejection ratio

PSRR is defined as the ratio of the change in input offset voltage due to the change in supply voltage producing it, keeping the other power supply voltage constant. It is also called as power supply sensitivity (PSV)

PSRR=

$$(\Delta v_{ios} / \Delta V_{cc})$$

|constant  $V_{EE}$  PSRR=  $(\Delta v_{ios} / \Delta V_{EE})$ |constant  $V_{cc}$

The typical value of PSRR for op-amp 741C is 30µV/V

### 13. Power

**Consumption**

It is the amount of quiescent power to be consumed by opamp with zero input voltage, for its proper functioning

It is denoted as P<sub>c</sub>

For 741C it is 85mW

### 14. Slew rate

It is defined as the maximum rate of change of output voltage with time. The slew rate is specified in V/µsec

Slew rate =

$$S = dV_o/dt|_{max}$$

It is specified by the op-amp in unity gain condition.

The slew rate is caused due to limited charging rate of the compensation capacitor and current limiting and saturation of the internal stages of op-amp, when a high frequency large amplitude signal is applied.

### Slew rate

It is given by  $dV_c/dt = I/C$

For large charging rate, the capacitor should be small or the current should be large.

$$S = I_{max}/C$$

For 741 IC the charging current is 15  $\mu$ A and the internal capacitor is 30 pF. S= 0.5V/ $\mu$ sec

### Slew rate equation

$$V_s = V_m \sin \omega t$$

$$V_o = V_m \sin \omega t$$

$$\frac{dVo}{dt} = V_m \omega \cos \omega t$$

S = slew rate =

$$\frac{dW}{dt}$$

max

$$S = V_m \omega = 2 \pi f V_m$$

$$S \neq 2 \pi f V_m V / sec$$

This is also called **full power bandwidth** of the op-amp

For distortion free output, the maximum allowable input frequency  $f_m$  can be obtained as

$$f_m = \frac{S}{2 \prod V_m}$$

# 15. Gain – Bandwidth product

It is the bandwidth of op-amp when voltage gain is unity (1). It is denoted as GB.

The GB is also called unity gain bandwidth (UGB) or closed loop bandwidth

It is about 1MHz for op-amp 741C

# 16. Equivalent Input Noise Voltage and Current

The noise is expressed as a power density

Thus equivalent noise voltage is expressed as V<sup>2</sup>/Hz

while the equivalent noise current is expressed as A<sup>2</sup>

/Hz

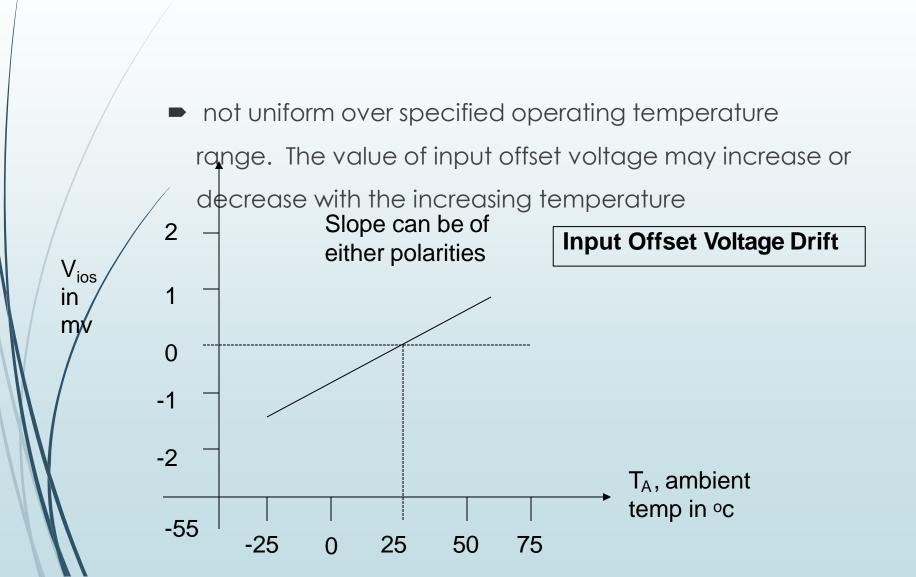

### 7. Average temperature coefficient of offset parameters

The average rate of change of input offset voltage per unit change in temperature is called average temperature coefficient of input offset voltage or input offset voltage drift

It is measured in  $\mu V/^{\circ}C$ . For 741 C it is 0.5  $\mu V/^{\circ}C$

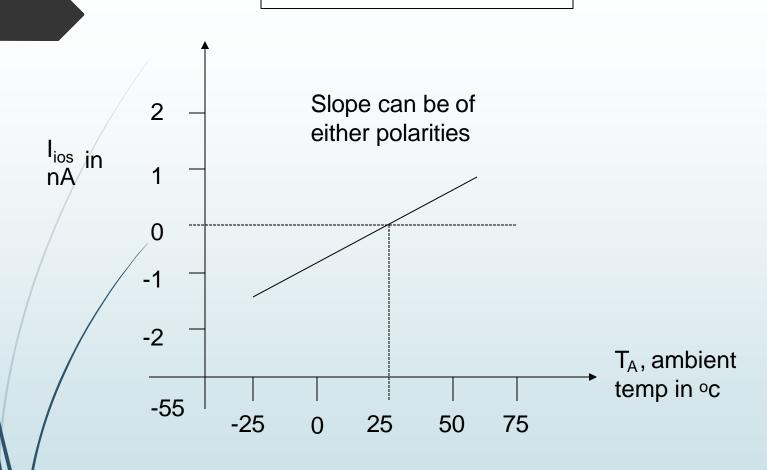

The average rate of change of input offset current per unit change in temperature is called average temperature coefficient of input offset current or input offset current drift

It is measured in nA/°C or pA/°C. For 741 C it is 12 pA/°C

### 18. Output offset voltage (Voos

The output offset voltage is the dc voltage present at the output terminals when both the input terminals are grounded.

It is denoted as Voos

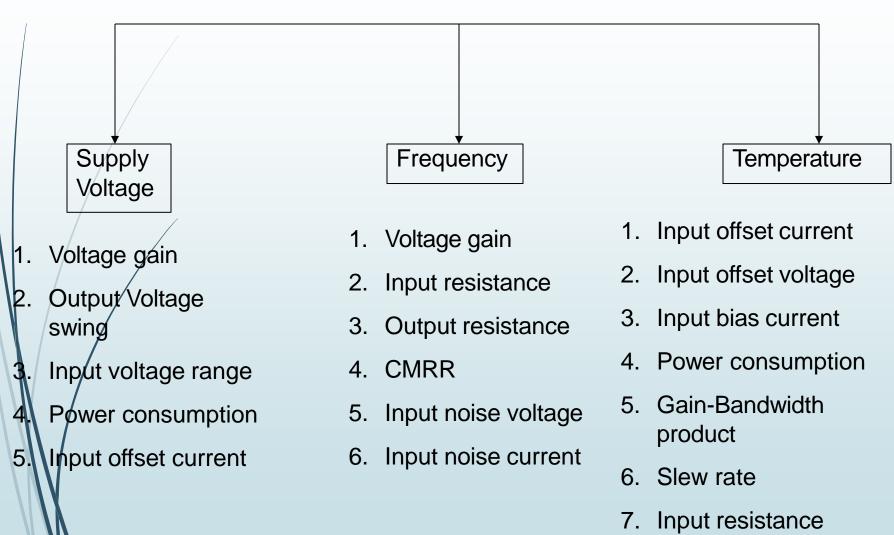

### **Factors affecting parameters of Op-amp**

# Parameter consideration for various applications

| For A.C. applications                   | For D.C. applications                   |

|-----------------------------------------|-----------------------------------------|

| Input resistance                        | Input resistance                        |

| Output resistance                       | Output resistance                       |

| Open loop voltage gain                  | Open loop voltage gain                  |

| Slew rate                               | Input offset voltage                    |

| Output voltage swing                    | Input offset current                    |

| Gain-bandwidth product                  | Input offset voltage and current drifts |

| Input noise voltage and current         |                                         |

| Input offset voltage and current drifts |                                         |

### Absolute Maximum Ratings of Opamp

Maximum power dissipation: This is the maximum power which can be dissipated, in the internal stages of the op-amp in the form of heat

Operating temperature range: As specified in the data sheet, op-amp can work satisfactorily, over the operating temperature range, as required for the given application

- Absolute Maximum Ratings of Opamp

- Maximum supply voltage: This is the maximum d.c. supply voltage which can be applied to the op-amp

Maximum differential input voltage: This rating gives the maximum value of difference between the two input voltages, applied to the two input terminals of the opamp

### Absolute Maximum Ratings of Opamp

Maximum common mode input voltage: This is the maximum value of the input voltage which can be simultaneously applied to the two input terminals

Storage temperature range: This gives the temperature range over which the op-amp can be stored safely.

# Op-amp characteristics dependent on the power supply voltages

- Absolute maximum power supply voltage

- Absølute maximum differential input voltages

- Absolute maximum common mode input voltage

### Ideal Op-amp:

- 1.An ideal op-amp draws nocurrent at both the input terminalsI.e.  $I_1 = I_2 = 0$ . Thus its input impedance is infinite. Any sourcecan drive it and there is no loading

- 2. The gain of an ideal op-amp is infinite, hence the on the driver stage differential input  $V_d = V_1 V_2$  is essentially zero for the finite output voltage  $V_o$

3. The output voltage V<sub>o</sub> is independent of the current drawn from the output terminals. Thus its output impedance is zero and hence output can drive an infinite number of other circuits

# The Ideal Operational Amplifier

$$A_{OL} = \infty$$

$$R_i = \infty$$

$$R_o = 0$$

Zero offset

$$(V_0 = 0 \text{ when } V_1 = V_2 = 0) V_{ios}$$

= 0

$$PSRR = 0$$

# Ideal Voltage transfer curve

## Practical voltage transfer curve

- 1. If  $V_d$  is greater than corresponding to b, the output

- attains +V<sub>sat</sub>

- 2. If V<sub>d</sub> is less than corresponding to a, the output attains

- $-V_{sat}$

- Thus range a-b is input range for which output varies linearily with the input. But  $A_{OL}$  is very high, practically this range is very small

### Equivalent circuit of practical opamp

A<sub>OL</sub> = Large signal open loop voltage gain

$V_d$  = Difference voltage  $V_1 - V_2$

$V_1$  = Non-inverting input voltage with respect to ground

$V_2$  = Inverting input voltage with respect to ground

R<sub>i</sub> = Input resistance of op-amp

R<sub>o</sub> = Output resistance of op-amp

### **Transient Response Rise time**

When the output of the op-amp is suddenly changing like pulse type, then the rise time of the response depends on the cut-off frequency  $f_H$  of the op-amp. Such a rise time is called cut-off frequency limited rise time or transient response rise time ( $t_r$ )

$$t_r = \frac{0.35}{f_H}$$

### Op-amp Characteristics

### DC Characteristics

Input bias current Input offset current Input offset voltage Thermal drift

### AC Characteristics

Slew rate Frequency response

### **DC Characteristics Thermal Drift**

The op-amp parameters input offset voltage  $V_{ios}$  and input offset current  $I_{ios}$  are not constants but vary with the factors

- 1. Temperature

- 2. Supply Voltage changes

- 3. Time

### Thermal Voltage Drift

It is defined as the average rate of change of input offset voltage per unit change in temperature. It is also called as input offset voltage drift

Input offset voltage drift =

$$\frac{\Delta V_{io\ s}}{\Delta T}$$

△V<sub>ios</sub> = change in input offset voltage

T = Change in temperature

### It is expressed in $\mu V/0$ c. The drift is not constant and it is

### Input bias current drift

It is defined as the average rate of change of input bias current per unit change in temperature

Thermal drift in input bias current =

$$\frac{\Delta I_b}{\Delta T}$$

It is measured in nA/°C or pA/°c. These parameters vary randomly with temperature. i.e. they may be positive in one temperature range and negative in another

### Input Offset current drift

It is defined as the average rate of change of input offset current per unit change in temperature

Thermal drift in input offset current =

$$\frac{\Delta I_{ios}}{\Delta T}$$

It is measured in nA/°C or pA/°c. These parameters vary randomly with temperature. i.e. they may be positive in one temperature range and negative in another

### Input Offset current Drift

### AC

### Characteristics

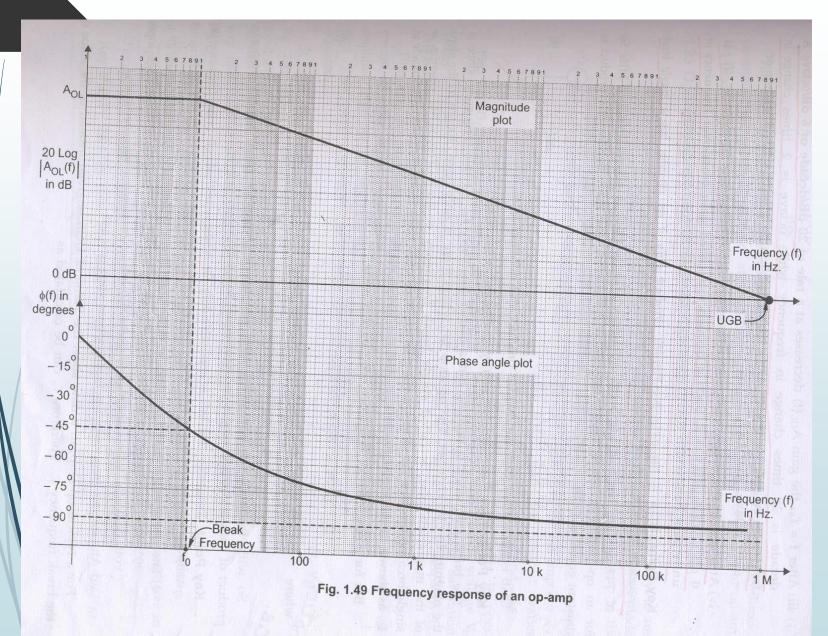

### Frequency Response

Ideally, an op-amp should have an infinite bandwidth but practically opamp gain decreases at higher frequencies. Such a gain reduction with respect to frequency is called as roll off.

The plot showing the variations in magnitude and phase angle of the gain due to the change in frequency is called **frequency response** of the op-amp

When the gain in decibels, phase angle in degrees are plotted against logarithmic scale of frequency, the plot is called **Bode Plot**

The manner in which the gain of the op-amp changes with variation in frequency is known as the *magnitude plot*.

The manner in which the phase shift changes with variation in frequency is known as the *phase-angle plot*.

# Obtaining the frequency response

To obtain the frequency response, consider the high frequency model of the op-amp with capacitor C at the output, taking into account the *capacitive effect* present

$$A_{OL}(f) = \frac{A_{OL}}{1 + j2\Pi f R_o C}$$

$$A_{OL}(f) = \frac{A_{OL}}{1 + j(\frac{f}{f_o})}$$

#### Where

A<sub>OL</sub>(f) = open loop voltage gain as a function of frequency

$A_{OL}$  = Gain of the op-amp at 0Hz F = operating frequency

$F_0$  = Break frequency or cutoff frequency of op-amp

For a given op-amp and selected value of C, the frequency fo is constant.

The above equation can be written in the polar form as

$$\left|A_{OL}(f)\right| = \frac{A_{OL}}{\sqrt{1 + \left| \left(\frac{f}{f_o}\right)\right|^2}}$$

$$\angle A_{OL}(f) = \Phi(f) = -\tan^{-1}\left|\left(\frac{f}{f_0}\right)\right|$$

### Frequency Response of an op-amp

The following observations can be made from the frequency response of an op-amp

- i)The open loop gain  $A_{\text{OL}}$  is almost constant from 0 Hz to the break frequency  $f_{\text{o}}$ .

- ii) At  $f=f_o$ , the gain is 3dB down from its value at 0Hz. Hence the frequency  $f_o$  is also called as -3dB frequency. It is also know as corner frequency iii) After  $f=f_o$ , the gain  $A_{OL}$  (f) decreases at a rate of 20 dB/decade or 6dB/octave. As the gain decreases, slope of the magnitude plot is

- iv)At a certain frequency, the gain reduces to 0dB. This means 20log|A<sub>OL</sub>| is

2ØdB/decade or -6dB/octave, after f=f<sub>o</sub>.

- 0dB i.e.  $|A_{OL}|$  =1. Such a frequency is called gain cross-over frequency or unity gain bandwidth (UGB). It is also called closed loop bandwidth.

- UGB is the gain bandwidth product only if an op-amp has a single breakover frequency, before A<sub>OL</sub> (f) dB is zero.

For an op-amp with single break frequency  $f_o$ , after  $f_o$  the gain bandwidth product is constant equal to UGB

UGB=A<sub>OL</sub> f<sub>o</sub>

UGB is also called gain bandwidth product and denoted as  $f_t$ Thus  $f_t$  is the product of gain of op-amp and bandwidth.

The break frequency is nothing but a corner frequency f<sub>o</sub>. Atthis frequency, slope of the magnitude plot changes. The op-amp for which there is only once change in the slope of the magnitude plot, is called single break frequency op-amp.

### For a single break frequency we can also write

$$UGB = A_f f_f$$

$A_f$  = closed loop voltage gain  $F_f$  =

bandwidth with feedback

The phase angle of an op-amp with single break frequency varies between 0° to 90°. The maximum possible phase shift is -90°, i.e. output voltage lags input voltage by 90° when phase shift is maximum

vi) At a corner frequency f=f<sub>o</sub>, the phase shift is -450.

| Frequency f in Hz     | $ A_{OL} $ (f)   in dB = 20 $\log \frac{A_{OL}}{\sqrt{1 + \left(\frac{f}{f_o}\right)^2}}$ in dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\phi (f) = -\tan^{-1}\left(\frac{f}{f_0}\right)$ |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 0                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in degrees                                        |

|                       | 106.02 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0°                                                |

| 5                     | 103.01 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - 45°                                             |

| 10                    | 99.03 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 63.43°                                          |

| 100                   | 79.98 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |

| 1000                  | 60.00 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 87.13°                                          |

| 100 × 10 <sup>3</sup> | SE VORDERNIT IN ON THE RESERVE OF TH | - 89.71°                                          |

|                       | 20.00 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 89.99°                                          |

| 1× 10 <sup>6</sup>    | 0 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 89.999°                                         |

Table 1.6

### The modes of using an opamp

- Open Loop: (The output assumes one of the two possible output states, that is +V<sub>sat</sub> or V<sub>sat</sub> and the amplifier acts as a switch only).

- Closed Loop: (The utility of an op-amp can be greatly increased by providing negative feed back. The output in this case is not driven into saturation and the circuit behaves in a linear manner).

# Open loop configuration of opamp

- The voltage transfer curve indicates the inability of opamp to work as a linear small signal amplifier in the open loop mode

- Such an open loop behaviour of the op-amp finds some rare applications like voltage comparator, zero crossing detector etc.

# Open loop op-amp configurations

- The configuration in which output depends on input, but output has no effect on the input is called open loop configuration.

- No feed back from output to input is used in such configuration.

- The opamp works as high gain amplifier

- The op-amp can be used in three modes in open loop configuration they are

- Differential amplifier

- Inverting amplifier

- 3. Non inverting amplifier

#### Differential Amplifier

The amplifier which amplifies the difference between the two input voltages is called differential amplifier.

$$V_o = A_{OL}V_d = A_{OL}(V_1 - V_2) = A_{OL}(V_{in1} - V_{in2})$$

Key point: For very small  $V_d$ , output gets driven into saturation due to high  $A_{OL}$ , hence this application is applicable for very small range of differential input voltage.

#### Inverting Amplifier

The amplifier in which the output is inverted i.e. having 180° phase shift with respect to the input is called an inverting amplifier

$$V_o = -A_{OL} V_{in2}$$

Keypoint: The negative sign indicates that there is phase shift of 180° between input and output i.e. output is inverted with respect to input.

#### Non-inverting Amplifier

The amplifier in which the output is amplified without any phase shift in between input and output is called non inverting amplifier

$$V_o = A_{OL} V_{in1}$$

Keypoint: The positive output shows that input and output are in phase and input is amplified  $A_{OL}$  times to get the output.

Why op-amp is generally not used in open loop mode? As open loop gain of op-amp is very large, very small input voltage drives the op-amp voltage to the saturation level. Thus in open loop configuration, the output is at its positive saturation voltage (+V<sub>sat</sub>) or negative saturation vøltage (-V<sub>sat</sub>) depending on which input V<sub>1</sub> or V<sub>2</sub> is more than the other. For a.c. input voltages, output may switch between positive and negative saturation voltages

This indicates the inability of op-amp to work as a linear small signal amplifier in the open loop mode. Hence the op-amp in open loop configuration is not used for the linear applications

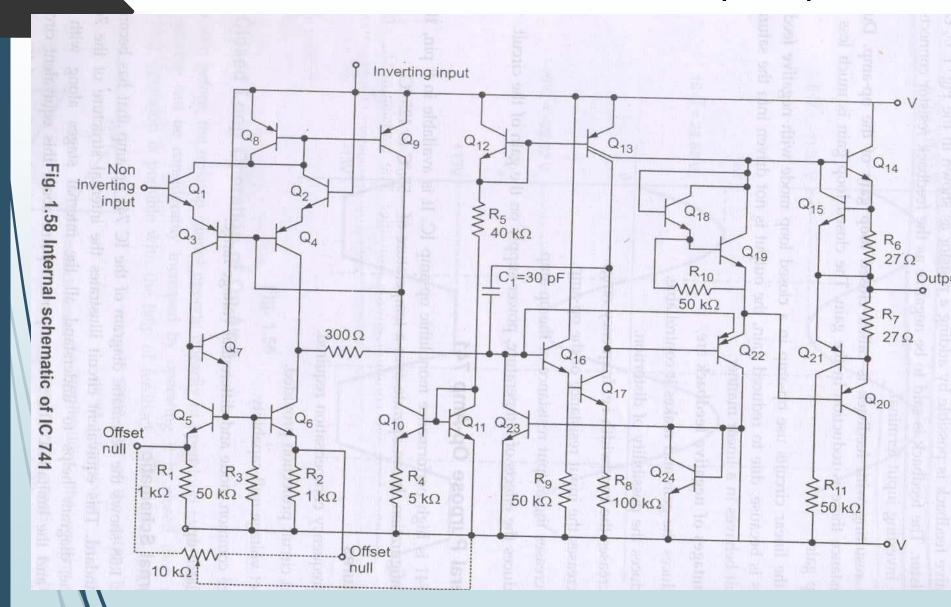

# General purpose op-amp

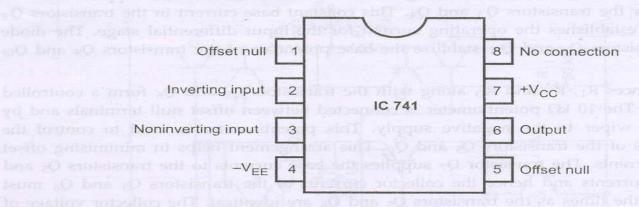

The IC 741 is high performance monolithic op-amp IC. It is available in 8pin, 10pin or 14pin configuration. It can operate over a temperature of -55°C to 125°C.

#### Features:

- i) No frequency compensation required

- ii) Short circuit protection provided

- ii) Offset Voltage null capability

- iv) Large common mode and differential voltage range

- v) No latch up

#### Internal schematic of 741 op-amp

#### The 8pin DIP package of IC 741

The 8 pin DIP package of IC 741 is shown in the Fig. 1.59.

Fig. 1.59 8 Pin diagram

#### 1.26.3 Ideal Vs Practical Characteristics of IC 741 Op-Amp

The Table 1.7 lists the ideal op-amp characteristics and the typical characteristics 741 IC, a popular general purpose op-amp IC.

| Sr. No    | Parameter              | Symbol           | Ideal      | Typical for 741 IC |

|-----------|------------------------|------------------|------------|--------------------|

| o -111' - | Open loop voltage gain | A <sub>OL</sub>  | ∞ ∞        | 2×10 <sup>5</sup>  |

| 2         | Output impedance       | Zout             | 0          | 75 Ω               |

| 3         | Input impedance        | Zin              | on ( ∞ ( ) | 2 ΜΩ               |

| 4         | Input offset current   | I <sub>ios</sub> | o ide      | 20 nA              |

| 5         | Input offset voltage   | Vios             | 0          | 1 mV               |

| 6         | Bandwidth              | B.W ·            | ∞          | 1 MHz              |

| . 7       | CMRR                   | etote Passi      | ed to      | 90 dB              |

| 8         | Slew rate              | S                | ∞ ===      | 0.5 V/μsec         |

| 9         | Input bias current     | I <sub>b</sub>   | 0          | 80 nA              |

| 10 PSRR   |                        | PSRR             | 0          | 30 μV/V            |

Table 1.7

#### Realistic simplifying assumptions

Zero input current: The current drawn by either of the input terminals (inverting and non-inverting) is zero

■ Virtual ground :This means the differential input voltage V<sub>d</sub> between the non-inverting and inverting terminals is essentially zero. (The voltage at the non inverting input terminal of an op-amp can be realistically assumed to be equal to the voltage at the inverting input terminal

# Closed loop operation of opamp:

The utility of the op-amp can be increased considerably by operating in closed loop mode. The closed loop operation is possible with the help of feedback. The feedback allows to feed some part of the output back to the/input terminals. In the linear applications, the opamp is always used with negative feedback. The hegative feedback helps in controlling gain, which otherwise drives the op-amp out of its linear range, even for a small noise voltage at the input terminals

## Unit - II

**■** Applications of OP-Amp

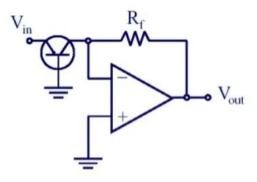

#### Ideal Inverting Amplifier

- 1. The output is inverted with respect to input, which is indicated by minus sign.

- 2. The voltage gain is independent of open loop gain of the op-amp, which is assumed to be large.

- The voltage gain depends on the ratio of the two resistances. Hence selecting  $R_f$  and  $R_1$ , the required value of gain can be easily obtained.

- 4. If  $R_f > R_{1,}$ , the gain is greater than 1 If  $R_f < R_{1,}$ , the gain is less than 1

- If  $R_{f} = R_1$ , the gain is unity

Thus the output voltage can be greater than, less than or equal to the input voltage in magnitude

- If the ratio of  $R_f$  and  $R_1$  is K which is other than one, the circuit is called scale changer while for  $R_f/R_1=1$  it is called phase inverter.

- 6. The closed loop gain is denoted as A<sub>VF</sub> or A<sub>CL</sub> i.e. gain with feedback

#### Ideal Non-inverting Amplifier

- 1. The voltage gain is always greater than one

- The voltage gain is positive indicating that for a.c. input, the output and input are in phase while for d.c. input, the output polarity is same as that of input

- The voltage gain is independent of open loop gain of op-amp, but depends only on the two resistance values

- The desired voltage gain can be obtained by selecting proper values of R<sub>f</sub> and R<sub>1</sub>

# Comparison of the ideal inverting and non-inverting op-amp

| Ideal Inverting amplifier                                                      | Ideal non-inverting amplifier                    |  |  |

|--------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| 1. Voltage gain=-R <sub>f</sub> /R <sub>1</sub>                                | 1. Voltage gain=1+R <sub>f</sub> /R <sub>1</sub> |  |  |

| 2. The output is inverted with respect to input                                | 2. No phase shift between input and output       |  |  |

| 3. The voltage gain can be adjusted as greater than, equal to or less than one | 3. The voltage gain is always greater than one   |  |  |

| 4. The input impedance is R <sub>1</sub>                                       | 4. The input impedance is very large             |  |  |

### Practical Inverting Amplifier

Closed Loop Voltage gain =

$$A_{CL} = -\frac{A_{OL}R_f}{R_1 + R_f + R_1A_{OL}}$$

#### Practical Non-Inverting Amplifier

Closed Loop Voltage gain =

$$A_{CL} = \frac{A_{CL} (R + R)}{R_1 + R_f + R_1 A_{OL}}$$

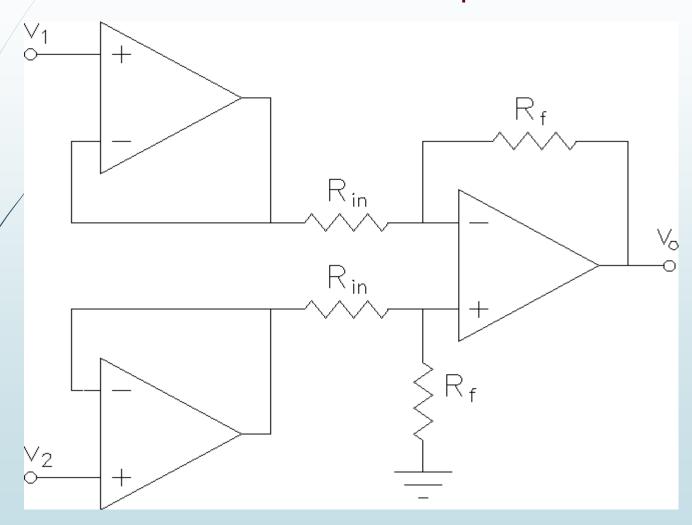

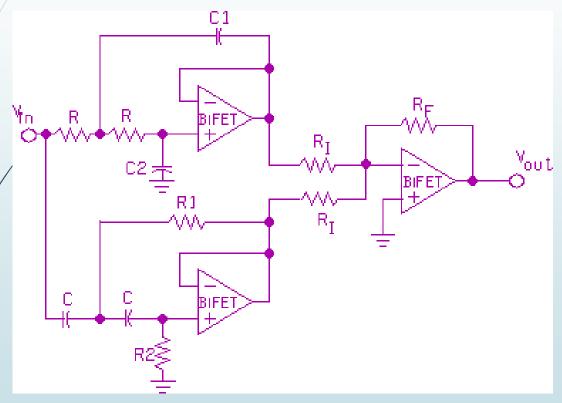

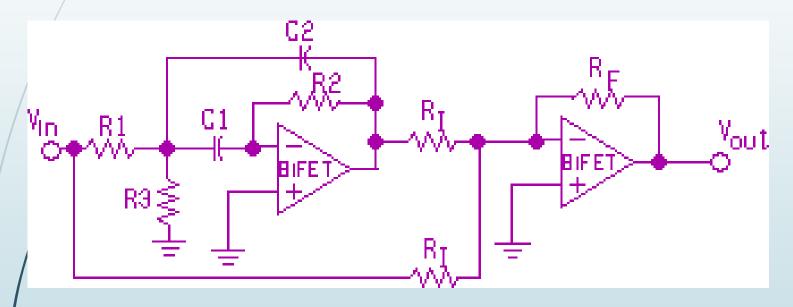

### Instrumentation Amplifier

In a number of industrial and consumer applications, the measurement of physical quantities is usually done with the help of transducers. The output of transducer has to be amplified So that it can drive the indicator or display system. This function is performed by an instrumentation amplifier

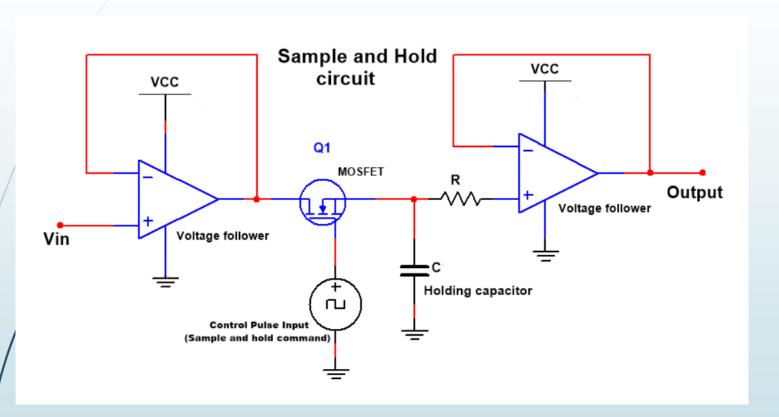

#### Sample Ans Hold Circuit

**Definition:** The Sample and Hold circuit is an electronic circuit which creates the samples of voltage given to it as input, and after that, it holds these samples for the definite time. The time during which sample and hold circuit generates the sample of the input signal is called sampling time.

Sample and Hold Circuit takes samples from the analog input signal and hold them for particular period of time and then outputs the sampled part of input signal. This circuit is only useful for sampling few microseconds of input signal. A Sample and Hold circuit consist of switching devices, capacitor and an operational amplifier.

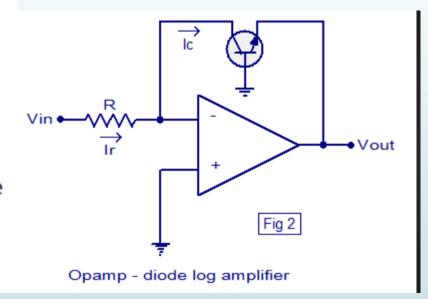

#### **Log and Antilog Amplifer**

#### Basic Antilog Amplifier

Vin is converted in to current  $I_c = I_{EBO}e^{Vin/K}$

$$V_{out} \cong -R_f I_{EBO} anti \ln \left( \frac{V_{in}}{0.025} \right)$$

- A transistor or a diode can be used as the input element.

- The operation of the circuit is based on the fact that V<sub>out</sub> = -R<sub>f</sub>I<sub>C</sub>, and I<sub>C</sub> = I<sub>EBO</sub>e<sup>Vin/K</sup> where K ≅ 0.025 V

- A logarithmic amplifier, or a log amplifier, is an electronic circuit that produces an output that is proportional to the logarithm of the applied input. This section discusses about the op-amp based logarithmic amplifier in detail.

- In the antilog amplifier, the input signal is at the inverting pin of the operational amplifier, which passes through a diode. As observed in the circuit shown above, the negative feedback is achieved by connecting the output to the inverting input terminal.

## Instrumentation Amplifier

## Features of instrumentation amplifier

- 1. high gain accuracy

- 2. high CMRR

- 3. high gain stability with low temperature coefficient

- 4/ low dc offset

- 5. low output impedance

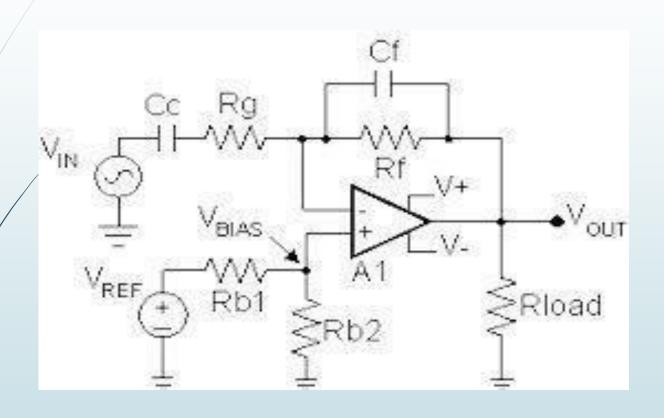

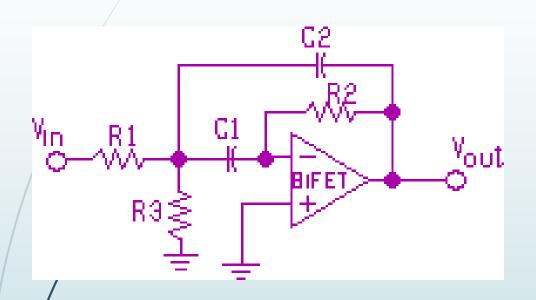

## **AC AMPLIFIER**

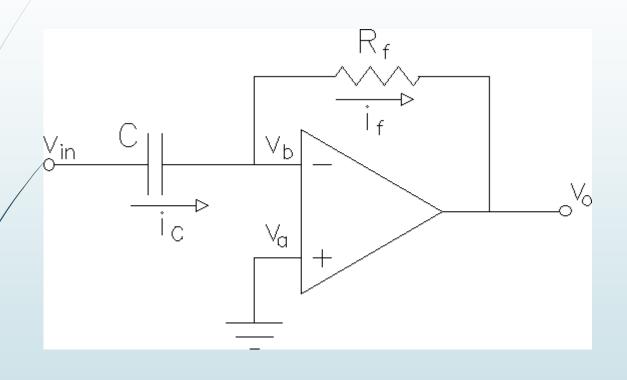

## Differentiator

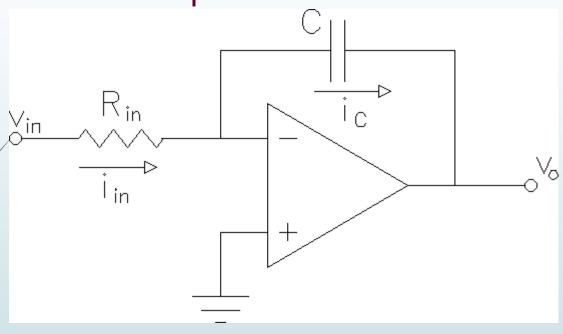

# Integrato

r

### Differential amplifier

This circuit amplifies only the difference between the two inputs. In this circuit there are two resistors labeled R <sub>IN</sub> Which means that their values are equal. The differential amplifier amplifies the difference of two inputs while the differentiator amplifies the slope of an input

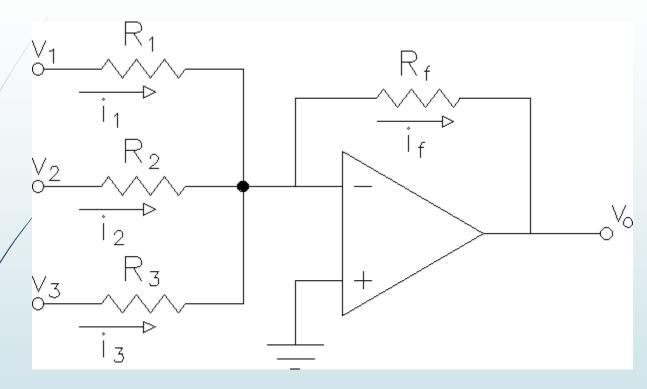

## Summer

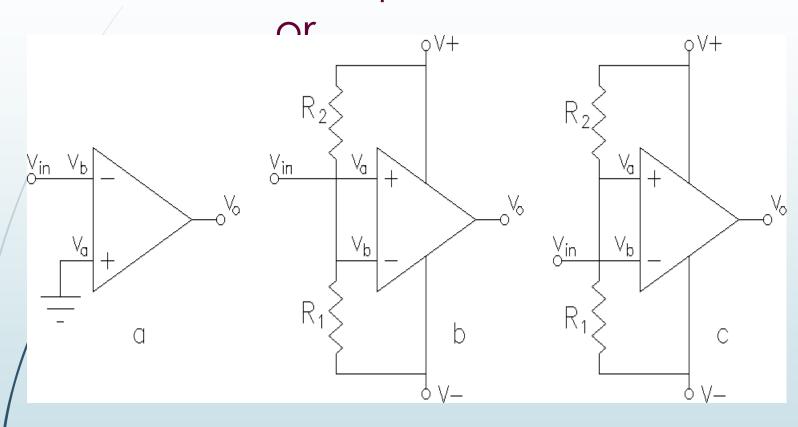

### Comparat

A comparator is a circuit which compares a signal voltage applied at one input of an op- amp with a known reference voltage at the other input. It is an open loop op - amp with output + Vsat

# Comparat

# Applications of comparator

- 1. Zero crossing detector

- 2. Window detector

- 3. Time marker generator

- 4. Phase detector

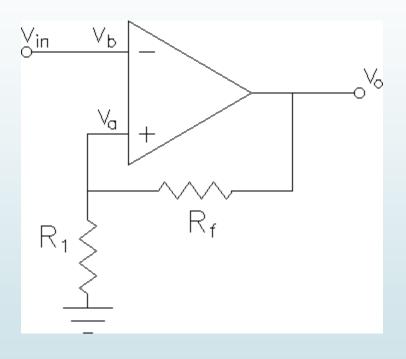

# Schmitt trigger

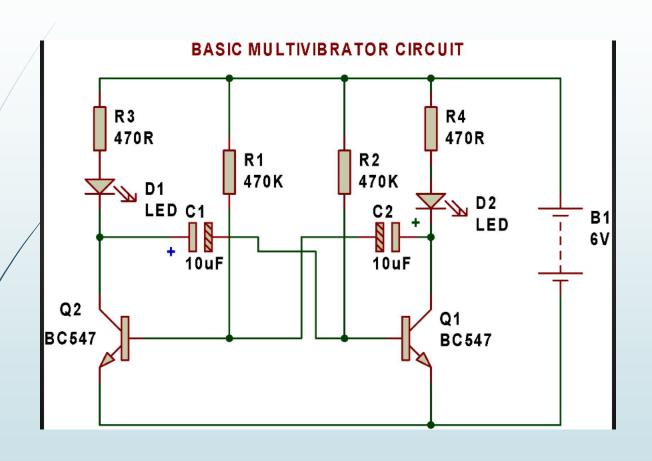

#### **Multivibrator Circuit:**

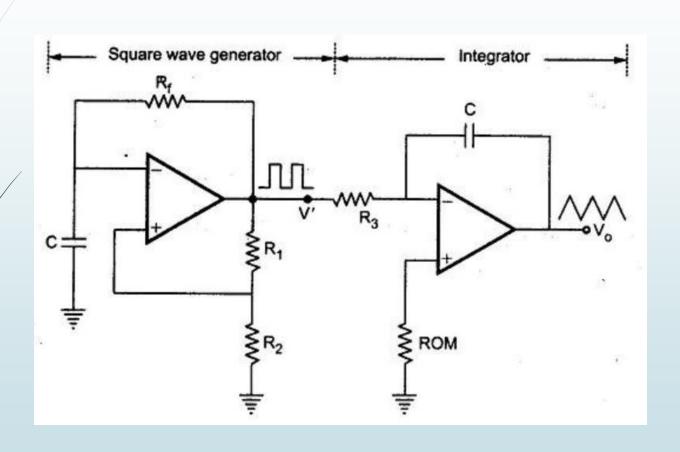

#### **Triangle Square Wave generator:**

#### **UNIT-III**

- Active filters

- Timer and phase locked loops

#### Filter

Filter is a frequency selective circuit that passes signal of specified Band of frequencies and attenuates the signals of frequencies outside the band

# Type of Filter

- 1. Passive filters

- 2. Active filters

#### Passive filters

Passive filters works well for high frequencies. But at audio frequencies, the inductors become problematic, as they become large, heavy and expensive. For low frequency applications, more number of turns of wire must be used which in turn adds to the series resistance degrading inductor's performance ie, low Q, resulting in high power dissipation

#### Active filters

Active filters used op- amp as the active element and resistors and capacitors as passive elements. By enclosing a capacitor in the feed back loop, inductor less active filters can be obtained

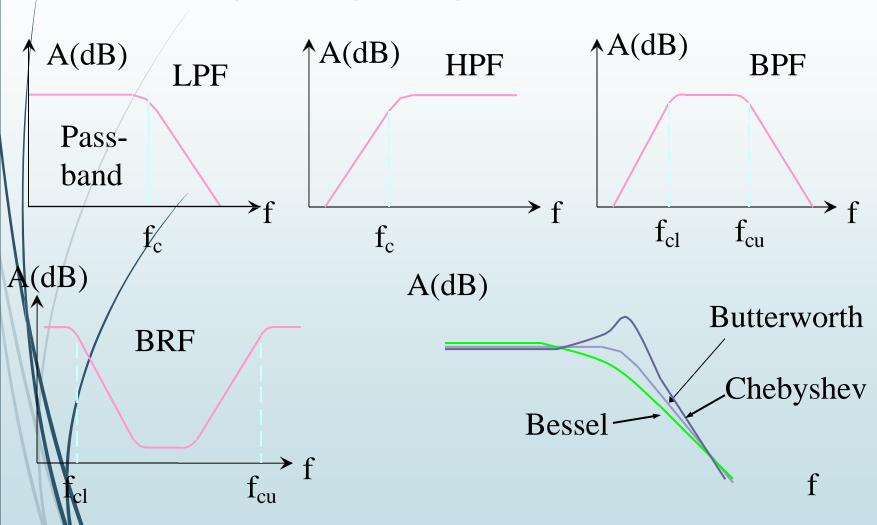

# some commonly used active filters

- Low pass filter

- 2. High pass filter

- 3. Band pass filter

- 4. Band reject filter

- 5. All pass filter

#### Active Filters

- Active filters use op-amp(s) and RC components.

- Advantages over passive filters:

- provide gain and overcome circuit losses

- □ in¢rease input impedance to minimize circuit loading

- higher output power

- sharp cutoff characteristics can be produced simply and efficiently without bulky inductors

- Single-chip universal filters (e.g. switched-capacitor ones) are available that can be configured for any type of filter or response.

# Review of Filter Types & Responses

- 4 major types of filters: low-pass, high-pass, band pass, and band-reject or band-stop

- 0 dB attenuation in the passband (usually)

- ■3 dB attenuation at the *critical* or *cutoff frequency*, f<sub>c</sub> (for Butterworth filter)

- Røll-off at 20 dB/dec (or 6 dB/oct) per pole outside the passband (# of poles = # of reactive elements).

Attenuation at any frequency f is:

atten.(dB) at

$$f = \log \left| \frac{f}{f_c} \right|$$

atten.(dB) at  $f_{dec}$

## Review of Filters (cont'd)

- Bandwidth of a filter: BW = f<sub>cu</sub> f<sub>cl</sub>

- Phase shift: 45º/pole at f<sub>c</sub>; 90º/pole at >> f<sub>c</sub>

- 4 types of filter responses are commonly used:

- □ Butterworth maximally flat in passband; highly nonlinear phase response with frequecny

- Bessel gentle roll-off; linear phase shift with freq.

- Chebyshev steep initial roll-off with ripples in passband

- □ Cauer (or elliptic) steepest roll-off of the four types but has ripples in the passband and in the stopband

## Frequency Response of Filters

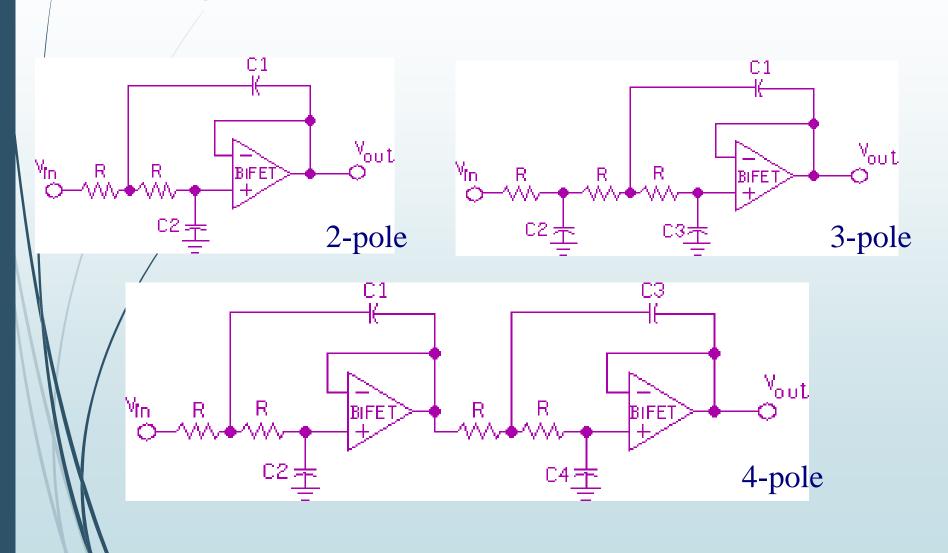

# Unity-Gain Low-Pass Filter Circuits

# Design Procedure for Unity-Gain LPF

- \* Determine/select number of poles required.

- $\triangle$  Calculate the frequency scaling constant,  $K_f = 2\pi f$

- \* Divide normalized C values (from table) by K<sub>f</sub> to obtain frequency-scaled C values.

- Select a desired value for one of the frequencyscaled Calues and calculate the impedance scaling factor:  $\frac{frequency - scaled \ C \ value}{K}$

- desired C value

- Divide all frequency-scaled C values by

$$K_{x}$$

Set

$$R = K_x \Omega$$

# An Example

Design a unity-gain LP Butterworth filter with a critical frequency of 5 kHz and an attenuation of at least 38 dB at 15 kHz.

The attenuation at 15 kHz is 38 dB

the attenuation at 1 decade (50 kHz) = 79.64 dB. We require a filter with a roll-off of at least 4 poles.  $K_f = 31,416$  rad/s. Let's pick  $C_1 = 0.01$   $\mu F$  (or 10 nF). Then  $C_2 = 8.54$  nF,  $C_3 = 24.15$  nF, and  $C_4 = 3.53$  nF. Pick standard values of 8.2 nF, 22 nF, and 3.3 nF.  $K_x = 3,444$

Make all R = 3.6 k $\Omega$  (standard value)

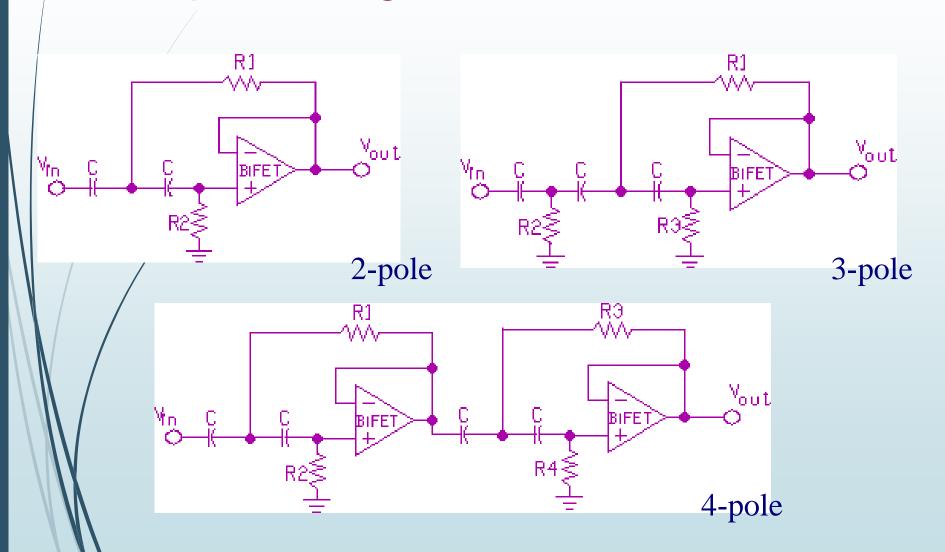

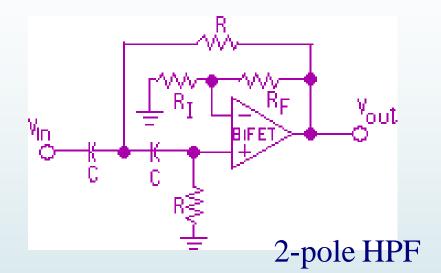

# Unity-Gain High-Pass Filter Circuits

# Design Procedure for Unity-Gain HPF

- The same procedure as for LP filters is used except for step #3, the normalized C value of 1 F is divided by K<sub>f</sub>. Then pick a desired value for C, such as 0.001 μF to 0.1 μF, to calculate K<sub>x</sub>. (Note that all capacitors have the same yalue).

- For step #6, multiply all normalized R values (from table) by K<sub>x</sub>.

- E.g. Design a unity-gain Butterworth HPF with a critical frequency of 1 kHz, and a roll-off of 55 dB/dec. (Ans.: C  $\pm$ 0.01  $\mu$ F, R<sub>1</sub> = 4.49 k $\Omega$ , R<sub>2</sub> = 11.43 k $\Omega$ , R<sub>3</sub> = 78.64 k $\Omega$ .; pick standard values of 4.3 k $\Omega$ , 11 k $\Omega$ , and 75 k $\Omega$ ).

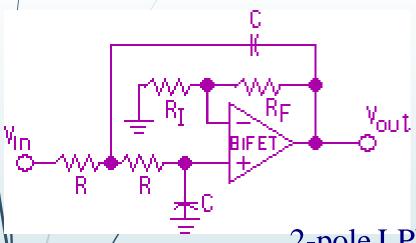

## Equal-Component Filter Design

2-pole LPF

Same value R & same value C

are used in

filter.

Select C

(e.g.  $0.01 \mu F$ ), then:

A<sub>v</sub> for # of poles is given in

a table and

is the same for

filter

$$A = \frac{R_F}{\text{de}_v \text{sign}} + 1$$

LPand HP

#### Exampl

e

Design an equal-component LPF with a critical frequency of 3 kHz and a roll-off of 20 dB/oct.

Minimum # of poles = 4

Choose C = 0.01  $\mu$ F;

® R = 5.3  $k\Omega$

From table,  $A_{v1}$  = 1.1523, and  $A_{v2}$  = 2.2346.

Choose  $R_{l1}$  =  $R_{l2}$  = 10  $k\Omega$ ; then  $R_{F1}$  = 1.5  $k\Omega$ , and  $R_{F2}$  = 12.3  $k\Omega$ .

Select standard values: 5.1 k $\Omega$ , 1.5 k $\Omega$ , and 12 k $\Omega$ .

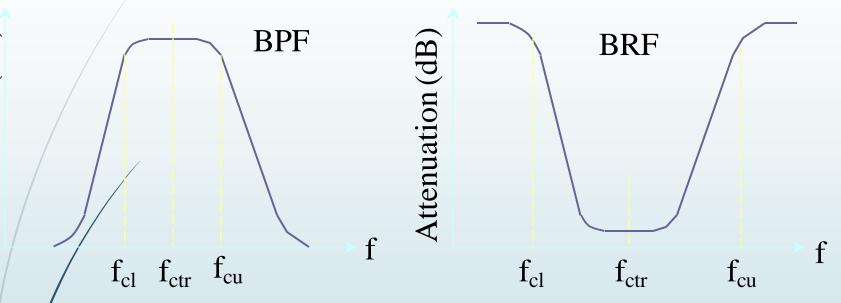

# Bandpass and Band-Rejection Filter

The quality factor, Q, of a filter is given by:

where

$$BW = f_{cu} - f_{cl}$$

and

$$f_{ctr} = \sqrt{f_{cu}f_{cl}}$$

$$Q = \frac{f_{ctr}}{BW}$$

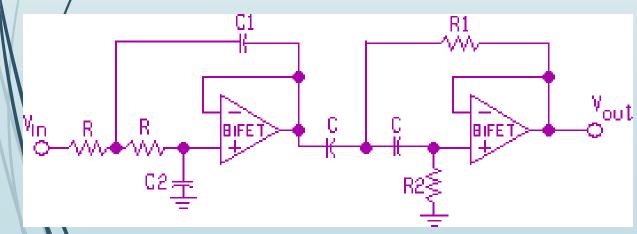

## More On Bandpass Filter

If BW and f are given, then:

A broadband BPF can be obtained by combining a LPF and

a HPF:

$$\int_{cl} \frac{BW^2}{4} + f_{ctr}^2 - \frac{BW}{2}; f_{cu} = \sqrt{\frac{BW^2}{4} + f_{ctr}^2 + \frac{BW}{2}}$$

The Q of this filter is usually

> 1.

# Broadband Band-Reject Filter

A LPF and a HPF can also be combined to give abroadband

**BRF**:

2-pole band-reject filter

#### Narrow-band Bandpass Filter

$$BW = \frac{f_{ctr}}{Q} = \frac{\Box 1}{Q}$$

$$C1 = C2 = C^{2\pi} R_1$$

$$R_2 = 2 R_1$$

$$R_3 = \frac{R_1}{2Q^2 - 1}$$

$$f_{ctr} = \frac{1}{2\sqrt{1 + \frac{R_1}{R_3}}} \sqrt{1 + \frac{R_1}{R_3}}$$

$$2\pi R_1$$

$R_3$  can be adjusted or trimmed to change f ctrwithout affecting the BW. Note that Q < 1.

# Narrow-band Band-Reject Filter

Filter

Easily obtained by combining the inverting output of a narrow-band BRF and the original signal:

The equations for R1, R2, R3, C1, and C2 are the same as before.  $R = R_F$  for unity gain and is often chosen to be >> R1.

# TRIANGULAR WAVE GENERATOR

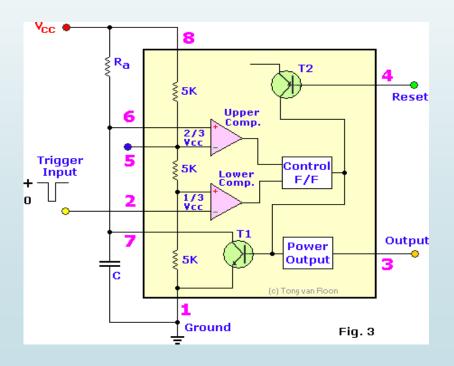

#### 555 IC

The 555 timer is an integrated circuit specifically designed to perform signal generation and timing functions.

#### Features of 555 Timer Basic blocks

- 1. It has two basic operating modes: monostable and astable

- It is available in three packages. 8 pin metal can,

8 pin dip, 14 pin dip.

- 3. /It has very high temperature stability

#### Applications of 555 Timer

- astable multivibrator

- 2. monostable multivibrator

- 3. Missing pulse detector

- 4. Linear ramp generator

- 5. / Frequency divider

- 6. Pulse width modulation

- 力. FSK generator

- 8. Pulse position modulator

- 9. Schmitt trigger

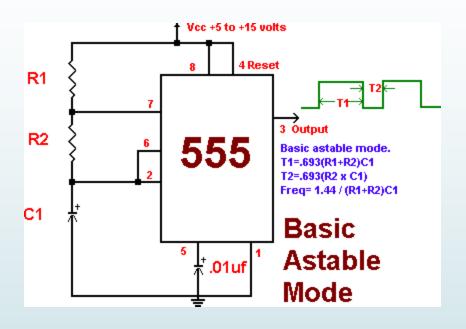

#### **Astable multivibrator**

#### Astable multivibrator

When the voltage on the capacitor reaches (2/3)Vcc, a switch is closed at pin 7 and the capacitor is discharged to (1/3)Vcc, at which time the switch is opened and the cycle starts over

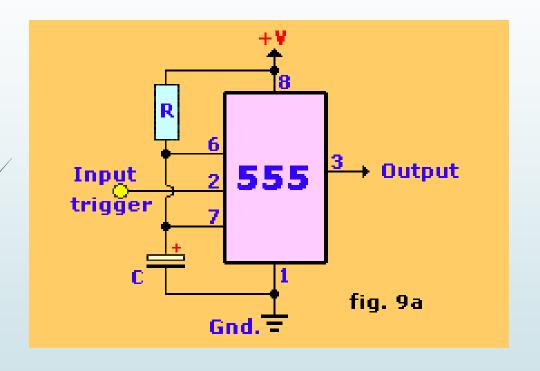

#### **Monostable multivibrator**

# Voltage controlled oscillator

A voltage controlled oscillator is an oscillator circuit in which the frequency of oscillations can be controlled by an externally applied voltage

#### The features of 566 VCO

- 1. Wide supply voltage range(10- 24V)

- 2. Very linear modulation characteristics

- 3. High temperature stability

#### Monolithic pll Ic:

#### MONOLITHIC PHASE LOCKED LOOPS (PLL IC 565) Pin Configuration of PLL IC 565: INPUT 12 NC VCO OUTPUT PHASE COMPARATOR VCO INTPUT EXTERNAL CAPACITOR FOR VCO REFERENCE 6 EXTERNAL RESISTOR FOR VCO DEMODULATED OUTPUT 14-Pin DIP Package Basic Block Diagram Representation of IC 565

#### Advantages of Monolith:

- The Advantages of using monoliths Monolithic applications are a natural way for an application to evolve. Most applications start out with a single objective or a small number of related objectives. Over time, features are added to the application to support business needs.

- It is generally used in multimedia, communication and in many other applications. There are two different types of PLL's – linear and nonlinear. The nonlinear is difficult and complicated to design in the real world, but the linear control theory is well modeled in analog PLL's.

#### **UNIT - IV**

- DATA CONVERTETRS

- VOLTAGE CONVERTS

#### Classification of ADCs

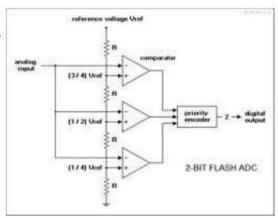

- Direct type ADC.

- 2. Integrating type ADC

## **Direct type ADCs**

- 1. Flash (comparator) type converter

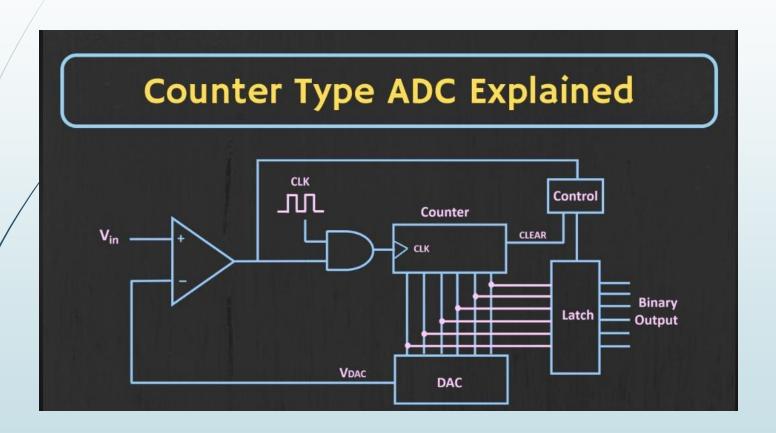

- 2. Counter type converter

- 3. Tracking or servo converter.

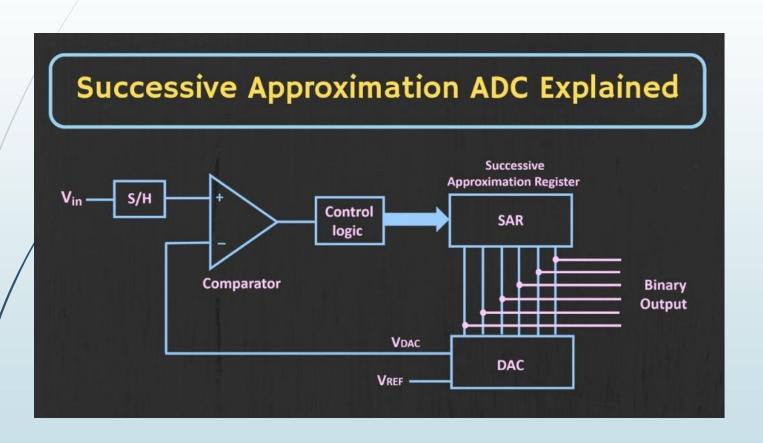

- Successive approximation type converter

## Integrating type converters

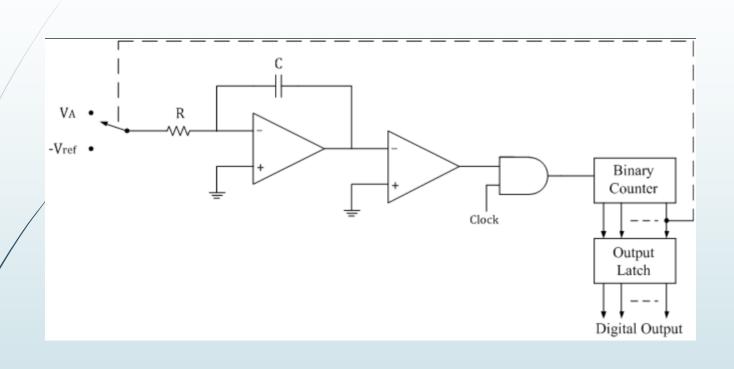

An ADC converter that perform conversion in an indirect manner by first changing the analog I/P signal to a linear function of time or frequency and then to a digital code is known as integrating type A/D converter

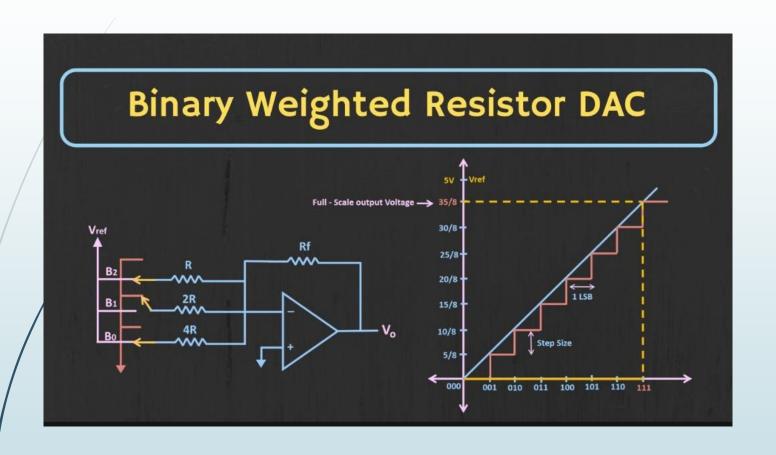

#### **Weighted Resistor DAC:**

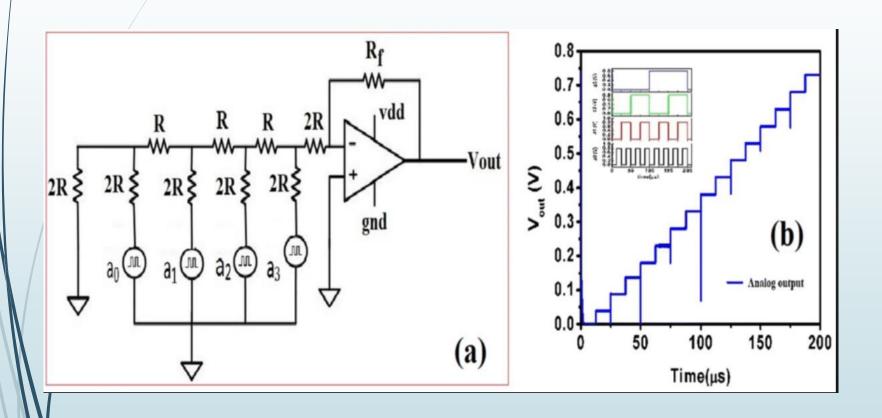

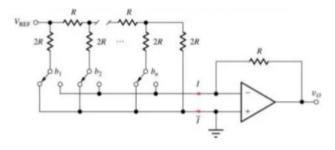

#### **R-2R Ladder DAC:**

#### **Inverted R-2R Ladder DAC:**

#### Inverted R-2R Ladder DAC

- · A very common DAC circuit architecture with good precision.

- Currents in the ladder and the reference source are independent of digital input. This contributes to good conversion precision.

- · Complementary currents are available at the output of inverted ladder.

- The "bit switches" need to have very low on-resistance to minimize conversion errors.

#### Parral type comparator:

| Analog input voltage V <sub>A</sub> volts                                                     | Comparator outputs |                |                | Priority encoder outputs |                |

|-----------------------------------------------------------------------------------------------|--------------------|----------------|----------------|--------------------------|----------------|

|                                                                                               | C <sub>3</sub>     | C <sub>2</sub> | C <sub>1</sub> | Y <sub>1</sub>           | Y <sub>0</sub> |

| 0 < V <sub>A</sub> < Vr/4                                                                     | 0                  | 0              | 0              | 0                        | 0              |

| Vr/4 <v<sub>A <vr 2<="" td=""><td>0</td><td>0</td><td>1</td><td>0</td><td>1</td></vr></v<sub> | 0                  | 0              | 1              | 0                        | 1              |

| Vr/2 <v<sub>A &lt; 3Vr/4</v<sub>                                                              | 0                  | 1              | 0              | 1                        | 0              |

| 3Vr/4 < V <sub>A</sub> < Vr                                                                   | 1                  | 1              | 1              | 1                        | 1              |

#### **Successive Approximation:**

#### ADC and Dual slope DAC:

#### **Counter type ADC:**

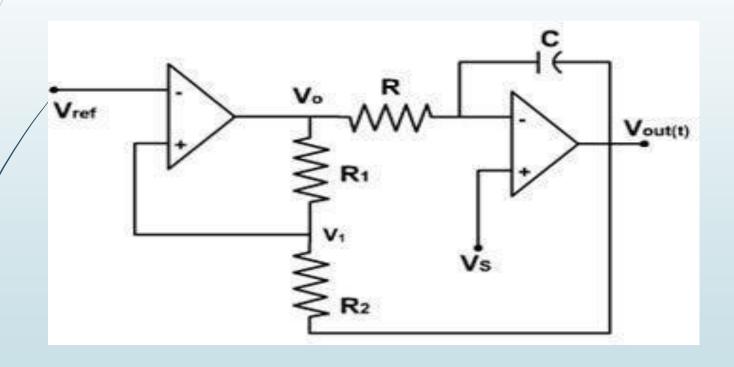

# INTRODUCTION TO VOLTAGE REGULATORS

A voltage regulator is designed to automatically maintain a constant voltage level. A voltage regulator may be a simple "feed-forward" design or may include negative feedback control loops. It may use an electromechanical mechanism, or electronic components.

#### IC Voltage Regulators:

- There are basically two kinds of IC voltage regulators:

- ☐ Multipin type, e.g. LM723C

- Multipin regulators are less popular but they provide the greatest flexibility and produce the highest quality voltage regulation

- 3-pin types make regulator circuit design simple

## Multipin IC Voltage Regulator

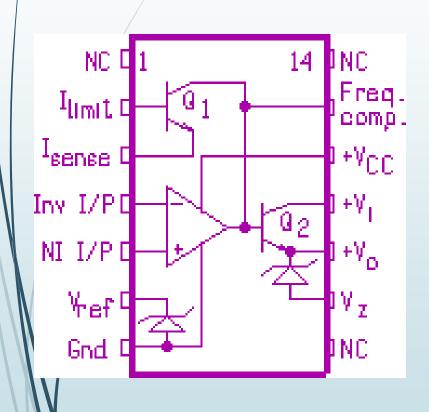

- The LM723 has an equivalent circuit that contains most of the parts of the op-amp voltage regulator discussed earlier.

- It has an internal voltage reference, error amplifier, pass transistor, and current limiter all in one IC package.

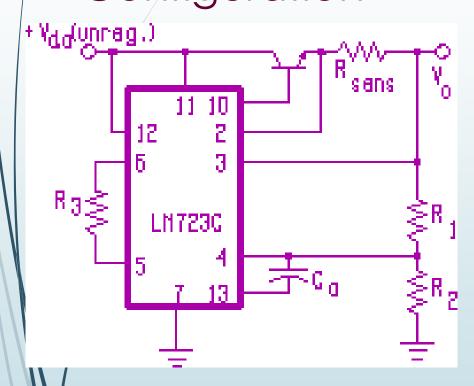

LM 723C Schematic

## LM723 Voltage Regulator

- Can be either 14-pin DIP or 10-pin TO-100 can

- May be used for either +ve or -ve, variable or fixed regulated voltage output

- Using the internal reference (7.15 V), it can operate as a high-voltage regulator with output from 7.15 V to about 37/V, or as a low-voltage regulator from 2 V to 7.15 V

- Max. output current with heat sink is 150 mA

- Propout voltage is 3 V (i.e.  $V_{CC} > V_{o(max)} + 3$ )

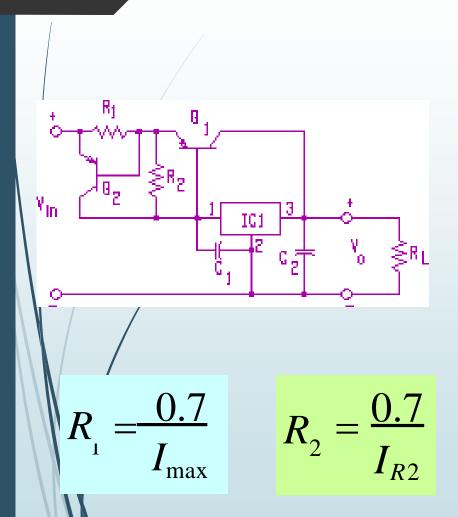

## M723 in High-Voltage Configuration

External pass transistor and current sensing added.

Design equations:

$$V_{o} = rac{V_{ref}(R_{+}+R_{-})}{R_{2}}$$

$$R_3 = \frac{R_1 R_2}{R_1 + R_2}$$

$R_{sens} = \frac{0.7}{I_{max}}$

Choose  $R_1 + R_2 = 10$   $k\Omega$ , and  $C_c = 100$  pF.

To make V<sub>o</sub> variable, replace R<sub>1</sub> with a pot.

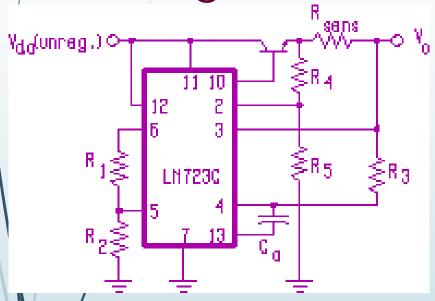

## M723 in Low-Voltage

Configuration

With external pass transistor and foldback current limiting

$$V_{o} = \frac{R_{2}V_{ref}}{R_{1} + R_{2}}$$

$$I_{L(max)} = \frac{R_4 V_0 + 0.7(R_4 + R_5)}{R_5 R_{sens}}$$

$$I_{\text{short}} = \frac{0.7(R_4 + R_5)}{R_5 R_{\text{sens}}}$$

$$R_{sens} = \frac{0.7V_o}{I_{short}(V_o + 0.7) - 0.7I_{L(max)}}$$

#### Under foldback condition:

$$V_{o}' = \frac{0.7R_{L}(R_{4} + R_{5})}{R_{S}R_{sens} - R_{4}R_{L}}$$

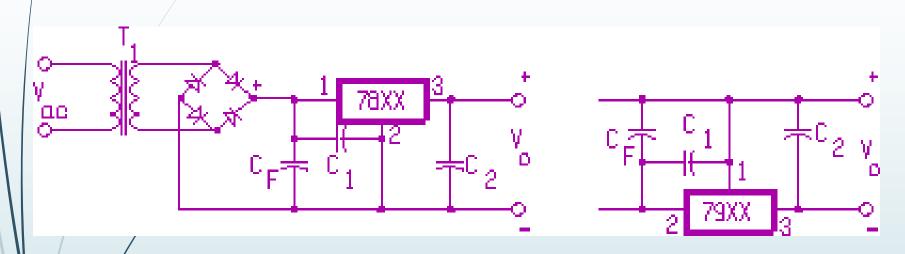

## Three-Terminal Fixed Voltage Regulators

- Less flexible, but simple to use

- Come in standard TO-3 (20 W) or TO-220 (15 W) transistor packages

- ■78/79XX series regulators are commonly available with 5, 6, 8, 12, 15, 18, or 24 V output

- Max. output current with heat sink is 1 A

- Built-in thermal shutdown protection

- 3-V dropout voltage; max. input of 37 V

- Regulators with lower dropout, higher in/output, and better regulation are available.

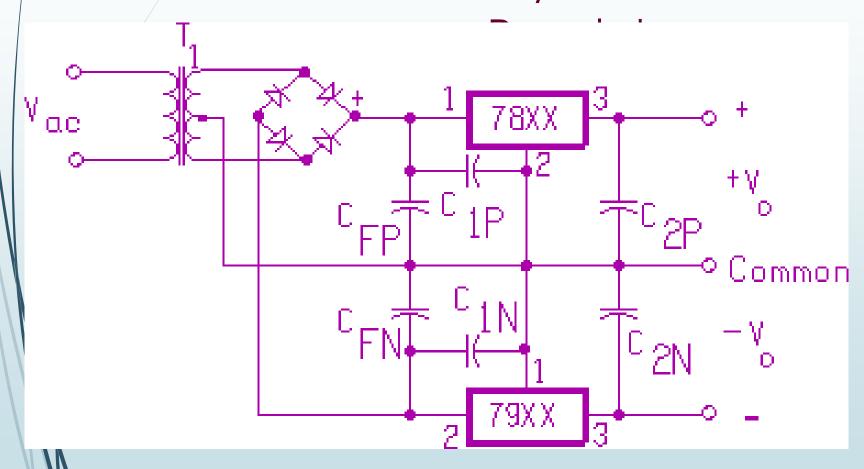

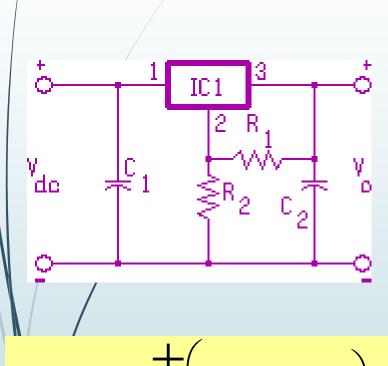

## Basic Circuits With 78/79XX Regulators

- Both the 78XX and 79XX regulators can be used to provide +ve or -ve output voltages

- $C_1$  and  $C_2$  are generally optional.  $C_1$  is used to cancel any inductance present, and  $C_2$  improves the transient response. If used, they should preferably be either 1  $\mu$ F tantalum type or 0.1  $\mu$ F mica type capacitors.

## Dual-Polarity Output with 78/79XX

## **78XX** Regulator with Pass Transistor

- $Q_1$  starts to conduct when  $V_{R2} = 0.7 \text{ V}$ .

- R2 is typically chosen so that max. I<sub>R2</sub> is 0.1 A.

- ■Power dissipation of  $Q_1$  is  $P = (V_i V_o)I_L$ .

- $Q_2$  is for current limiting protection. It conducts when  $V_{R1} = 0.7$  V.

- Q<sub>2</sub> must be able to pass max. 1 A; but note that max. V<sub>CE2</sub> is only 1.4 V.

### 78XX Floating Regulator

$$V_o = V_{reg} + \left( \frac{1}{R_1} + I_Q \right) R_2$$

- It is used to obtain an output > the V<sub>reg</sub> value up to a max.of 37 V.

- $R_1$  is chosen so that  $R_1 \stackrel{>}{\sim} 0.1$   $V_{\text{reg}} I_{Q}$ , where I is the

## 3-Terminal Variable Regulator

- The floating regulator could be made into a variable regulator by replacing R₂ with a pot. However, there are several disadvantages:

- ☐ Minimum output voltage is V<sub>reg</sub> instead of 0 V.

- $\Box$  I/Q is relatively large and varies from chip to chip.

- Power dissipation in R<sub>2</sub> can in some cases be quite large resulting in bulky and expensive equipment.

- A variety of 3-terminal variable regulators are available, g. LM317 (for +ve output) or LM 337 (for -ve output).

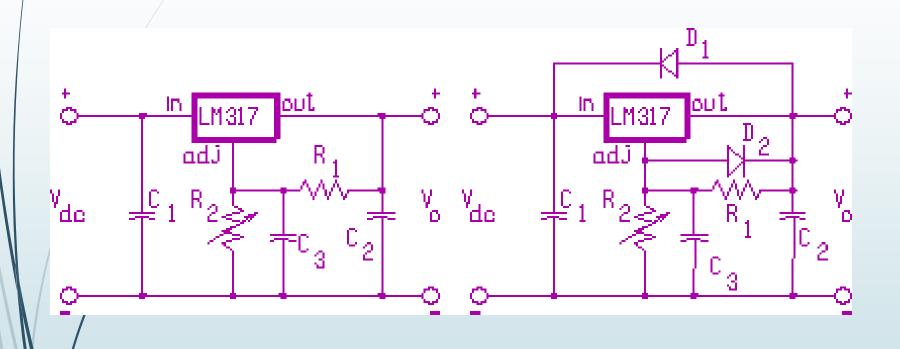

## Bosic LM317 Variable Regulator Circuits

Circuit with capacitors to improve performance

(a)

Circuit with protective diodes

(b)

#### Notes on Basic LM317 Circuits

- The function of C<sub>1</sub> and C<sub>2</sub> is similar to those used in the 78/79XX fixed regulators.

- $\blacksquare$   $C_3$  is used to improve ripple rejection.

- Protective diodes in circuit (b) are required for highcurrent/high-voltage applications.

$$V_o = V_{ref} + \left(\frac{V}{R_1} + I_{adj}\right)R_2$$

$$R_2 = \frac{R \left( V - V \right)}{V_{ref} + I_{adj} R_1}$$

$V_o = V_{ref} + \begin{pmatrix} V_{ref} + I_{adj} \end{pmatrix} R_2$  where  $V_{ref} = 1.25$  V, and  $I_{adj}$  is the current flowing into the adj. terminal (typically 50 µA).

$R_2 = \frac{1 - o - ref}{V_{ref} + I_{adi}R_1}$   $R_1 = V_{ref} / I_{L(min)}, \text{ where } I_{L(min)} \text{ is}$ typically 10 m/s

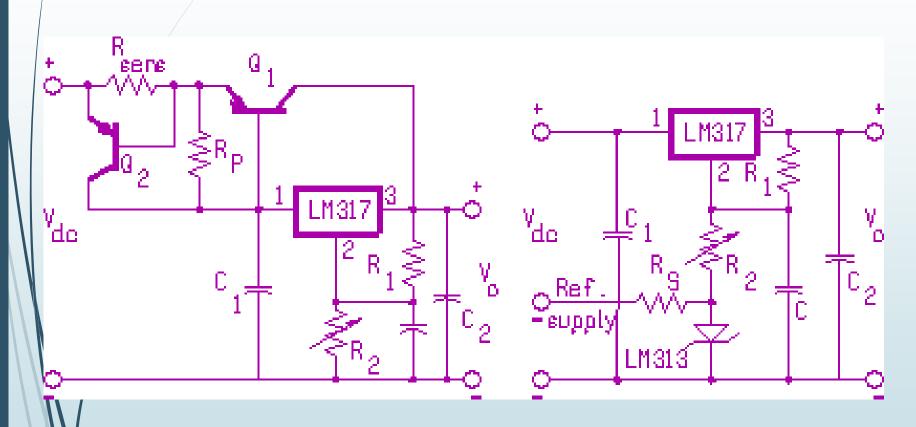

### LM317 Regulator Circuits

Circuit with pass transistor and current limiting

Circuit to give 0V min. output voltage

#### **UNIT-V**

- Digital Logic families

- CMOS Logic

- Combinational circuits

- Sequnitional circuits

### Overview

- Integration, Moore's law

- Early families (DL, RTL)

- TTL

- Evolution of TTL family

- ECL

- CMOS family and its evolution

- Overview

## **Integration Levels**

- Gate/transistor ratio is roughly 1/10

- SSI < 12 gates/chip

- MSI < 100 gates/chip</p>

- LSI ...1K gates/chip

- -/VLSI/ ...10K gates/chip

- → UL∕SI ...100K gates/chip

- GSI ...1Meg gates/chip

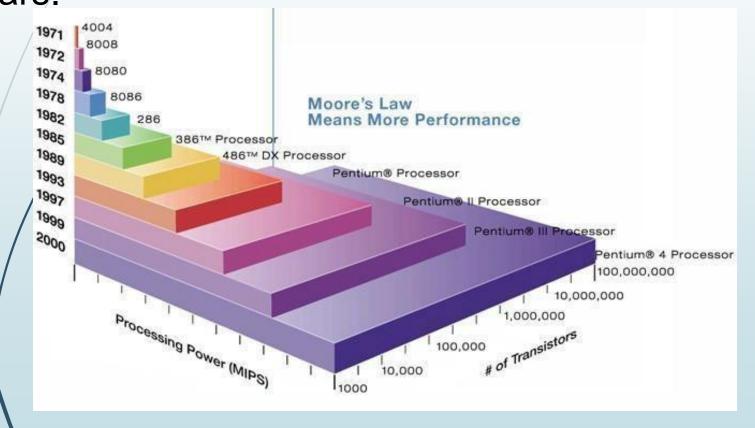

### Moore's law

A prediction made by Moore (a co-founder of Intel) in 1965: "... a number of transistors to double every 2 years."

## In the beginning...

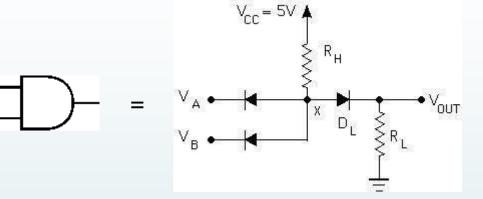

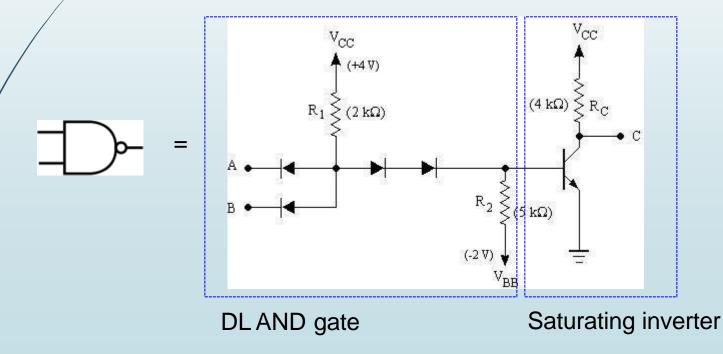

#### Diode Logic (DL)

- •simplest; does not scale

- NOT not possible (need an active

- eRleesmisetnotr)-

- Transistor Logic (RTL)

- replace diode switch with a transistor switch

- can be cascaded

- large power draw

#### was...

#### Diode-Transistor Logic (DTL)

- essentially diode logic with transistor amplification

- reduced power consumption

- •faster than RTL

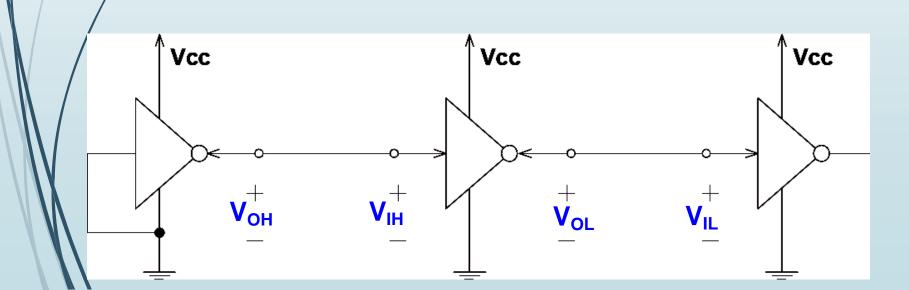

## Logic families: V levels

V<sub>OH</sub>(min) – The minimum voltage level at an output in the logical "1" state under defined load conditions

V<sub>OL</sub>(max) – The maximum voltage level at an output in the logical "0" state under defined load conditions

V<sub>IH</sub>(min) – The minimum voltage required at an input to be recognized as "1" logical state

V<sub>IL</sub>(max) – The maximum voltage required at an input that still will be recognized as "0" logical state

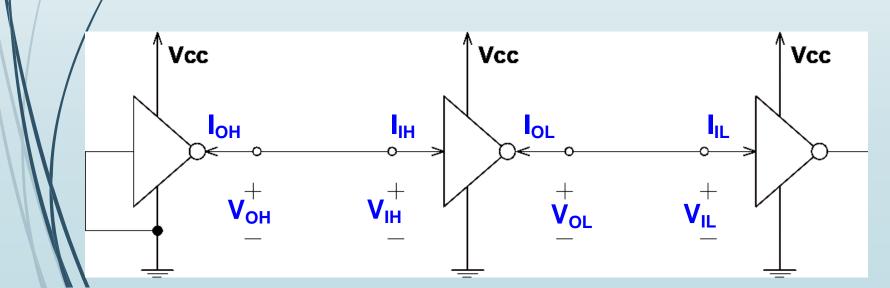

## Logic families: I requirements

I<sub>OH</sub> – Current flowing into an output in the logical "1" state under specified load conditions

I<sub>OL</sub> – Current flowing into an output in the logical "0" state under specified load conditions

$I_{IH}$  – Current flowing into an input when a specified HI level is applied to that input  $I_{IL}$  – Current flowing into an input when a specified LO level is applied to that input

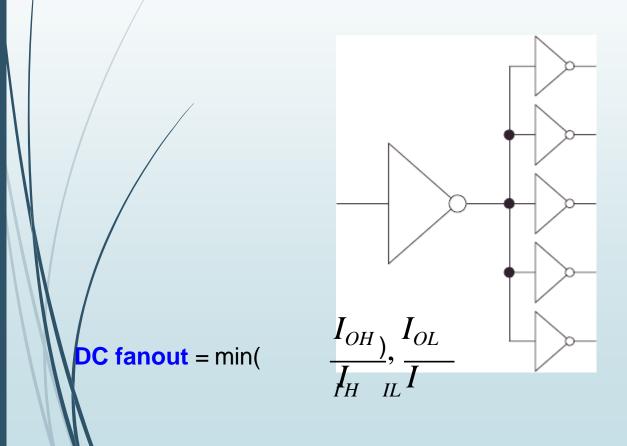

## Logic families: fanout

Fanout: the maximum number of logic inputs (of the same logic family) that an output can drive reliably

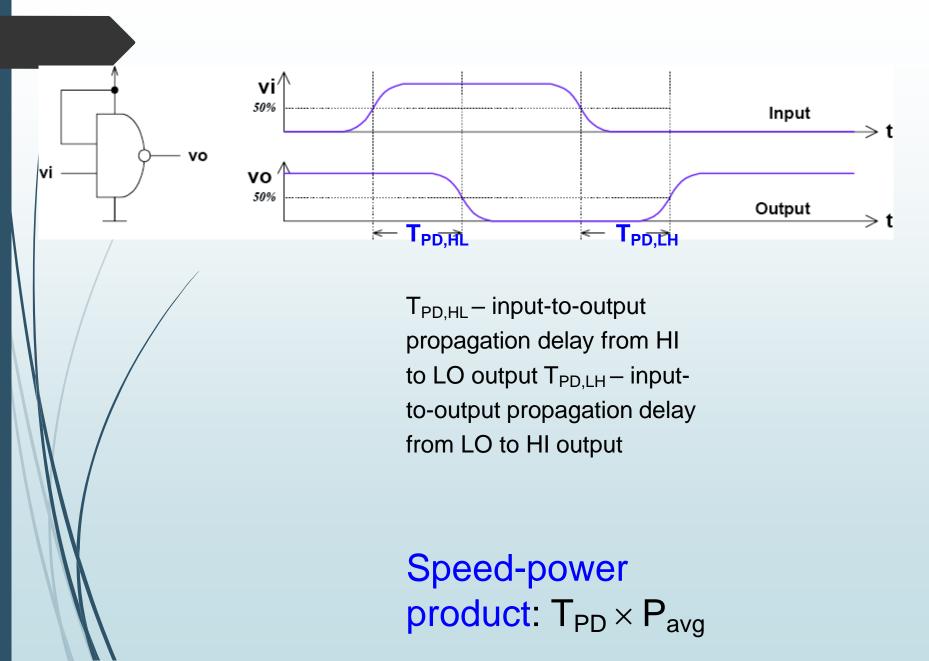

## Logic families: propagation delay

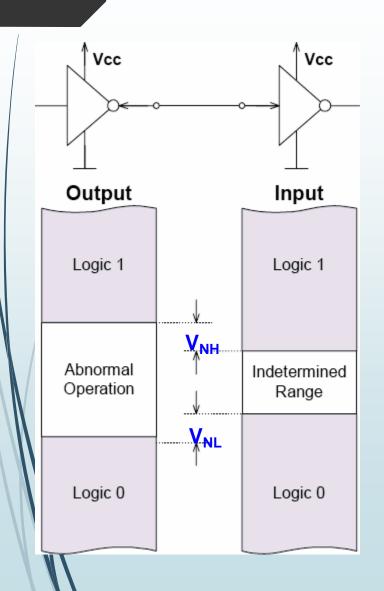

## Logic families: noise margin

HI state noise margin:  $V_{NH} = V_{OH}(min) - V_{IH}(min)$

LO state noise margin:  $V_{NL} = V_{IL}(max) - V_{OL}(max)$

Noise margin:  $V_N = min(V_{NH}, V_{NL})$

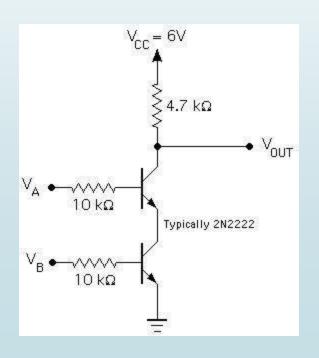

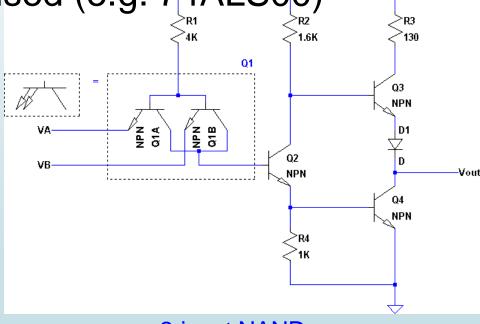

#### Bipolar Transistor-Transistor Logic (TTL)

- •first introduced by in 1964 (Texas Instruments)

- TTL has shaped digital technology in many ways

- Standard TTL family (e.g. 7400) is obsolete

- Newer TTL families still used (e.g. 74ALS00)

#### Distinct features

- Multi-emitter transistors

- Totem-pole transistor

- arrangement

- Open LTspice example:

TT\\NAND...

2-input NAND

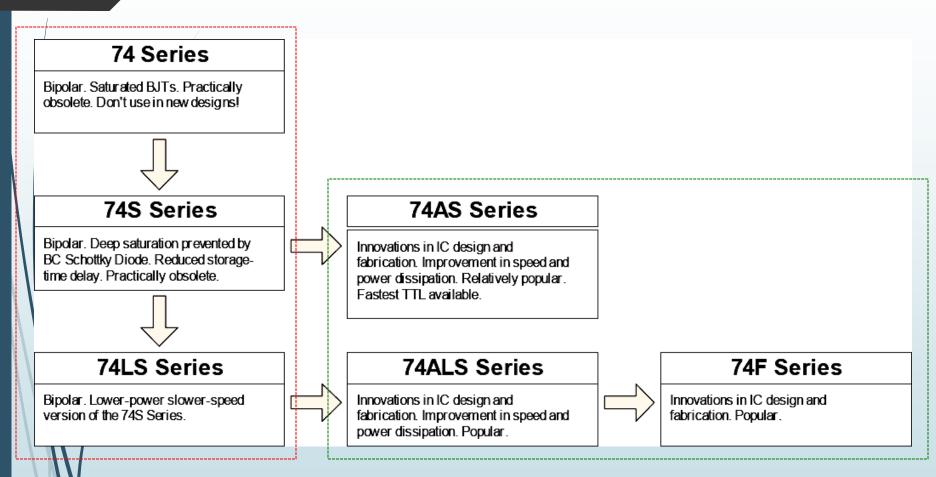

### **ITL** evolution

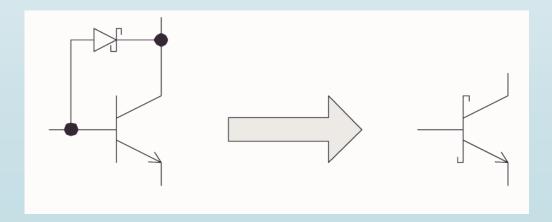

#### \$chottky series (74LS00) TTL

- •A major slowdown factor in BJTs is due to transistors going in/out of saturation

- Shottky diode has a lower forward bias (0.25V)

- When BC junction would become forward biased, the Schottky diode bypasses the current preventing the transistor from going into saturation

## **ITL** family evolution

Legacy: don't use in new designs

Widely used today

### **ECL**

#### Emitter-Coupled Logic (ECL)

- •PROS: Fastest logic family available (~1ns)

- CONS: low noise margin and high power dissipation

- Operated in emitter coupled geometry (recall differential amplifier or emitter-follower), transistors are biased and operate near their Qpoint (never near saturation!)

- Logic levels. "0": -1.7V. "1": -0.8V

- •Such strange logic levels require extra effort when interfacing to TTL/CMOS logic families.

- Open LTspice example: ECL inverter...

### **CMOS**

### Complimentary MOS (CMOS)

- Other variants: NMOS, PMOS (obsolete)

- Very low static power consumption

- Scaling capabilities (large integration all MOS)

- Full swing: rail-to-rail output

- Things to watch out for:

- don't leave inputs floating (in TTL these will float

- to HI, in CMOS you get undefined behaviour)

- -susceptible to electrostatic damage (finger of death)

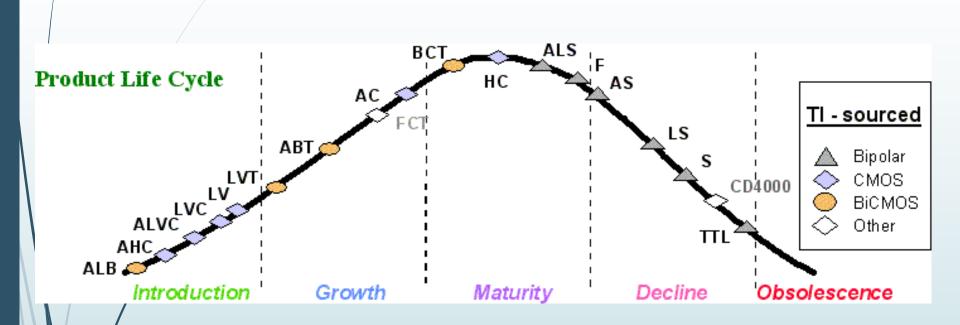

## Life-cycle

### Outline

- Boolean Algebra

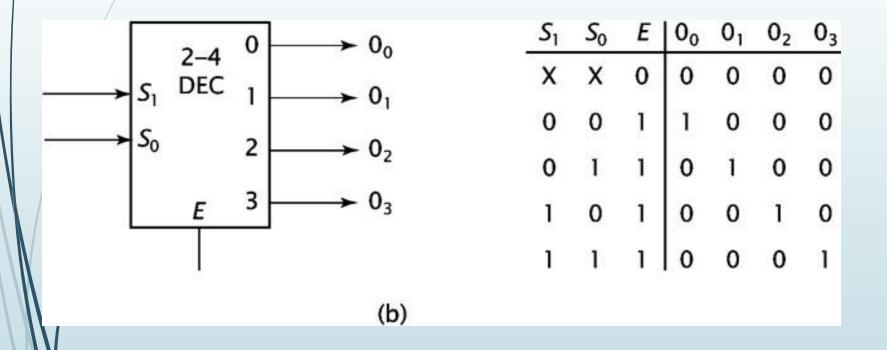

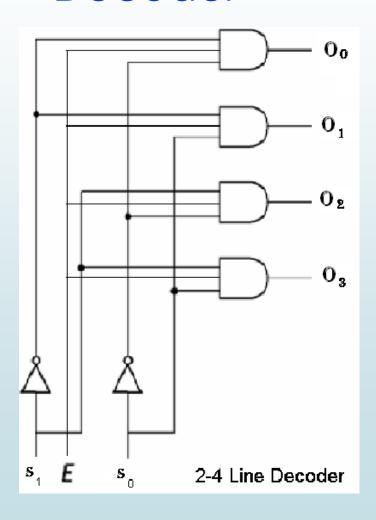

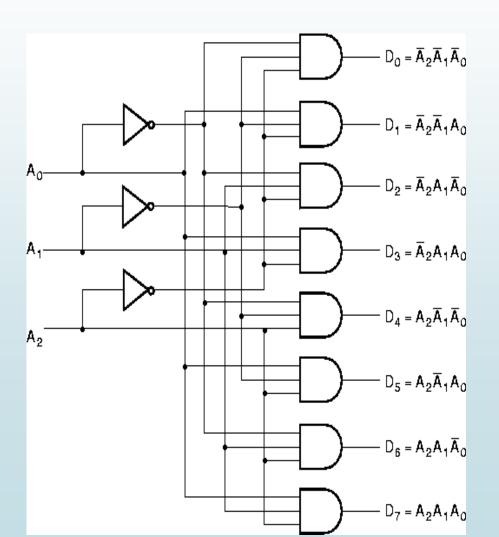

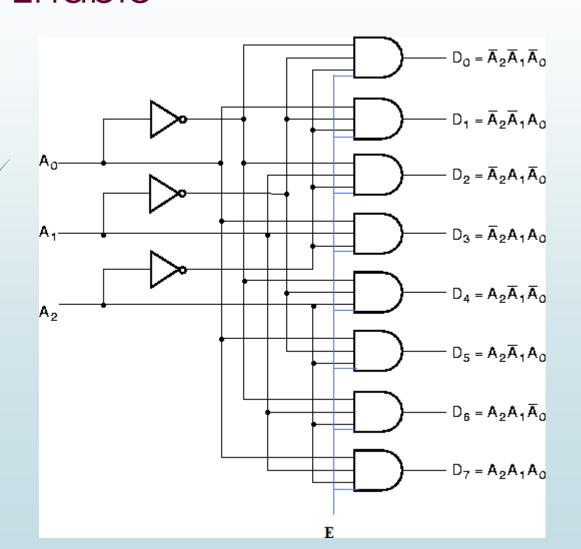

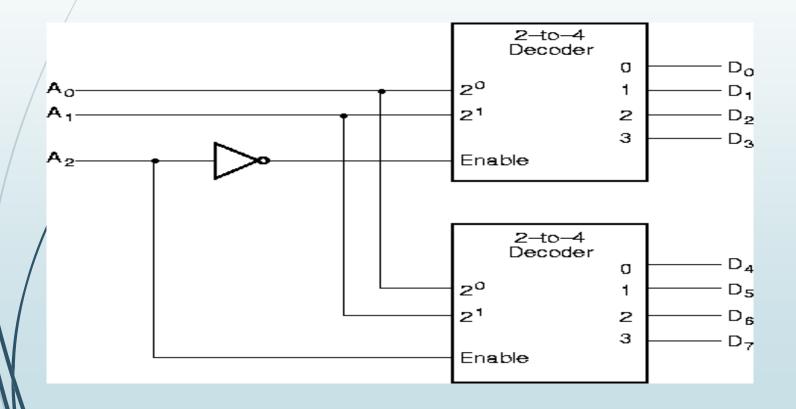

- Decoder

- Encoder

- MUX

## History: Computer and the Rationalist

- Modern research issues in AI are formed and evolve through a combination of historical, social and cultural pressures.

- The rationalist tradition had an early proponent in Plato, and was continued on through the writings of Pascal, Descates, and Liebniz

- For the rationalist, the external world is reconstructed through the clear and distinct ideas of a mathematics

## History: Development of Formal Logic

- The goal of creating a formal language for thought also appears in the work of <u>George</u> <u>Boole</u>, another 19<sup>th</sup> century mathematician whose work must be included in the roots of Al

- The importance of Boole's accomplishment is in the extraordinary power and simplicity of the system he devised: Three Operations

### Three Operations

three basic Boolean operations can be defined arithmetically as follows.

$$\square x \cap y = xy$$

Figure 1. Truth tables

| X | у | x∧y | x∨y |  |

|---|---|-----|-----|--|

| 0 | 0 | 0   | 0   |  |

| 1 | 0 | 0   | 1   |  |

| 0 | 1 | 0   | 1   |  |

| 1 | 1 | 1   | 1   |  |

## Boolean function and logic diagram

Boolean algebra: Deals with binary variables and logic operations operating on those variables.

Logic diagram: Composed of graphic symbols for logic gates. A simple circuit sketch that represents inputs and outputs of Boolean functions.

### Basic Identities of Boolean Algebra

```

(1) \qquad x + 0 = x

(2) x \cdot 0 = 0

(3) x + 1 = 1

(4) x \cdot 1 = 1

(5) x + x = x

(6) x \cdot x = x

(7)x + x' = x

(8) x \cdot x' = 0

(9) x + y = y + x

(10)xy = yx

(11) x + (y + z) = (x + y) + z

(12)x (yz) = (xy) z