#### **VEMU INSTITUTE OF TECHNOLOGY**

P.KOTHAKOTA, NEAR PAKALA, CHITTOOR-517112

(Approved by AICTE, New Delhi & Permanently Affiliated to JNTUA, Accredited by NAAC, Recognised under 2(F) &12(B)of UGC Act 1956,An ISO 9001:2015 certified Institute)

#### NAME: S VIDYA

#### SUBJECT: DLD (20A04303T)

#### REGULATION: R20

#### UNIT-1 LIST OF CONTENTS

#### **BINARY NUMBER SYSTEM**

- BINARY NUMBERS

- OCTAL NUMBERS

- HEXA DECIMAL NUMBERS

- NUMBER BASE CONVERSIONS

- COMPLIMENTS

- SIGNED BINARY NUMBERS

- BINARY CODES

## LOGIC SIMPLIFICATION

Binary logic and Gates

#### Boolean Algebra

- Basic Properties

- Algebraic Manipulation

- Standard and Canonical Forms

- Minterms and Maxterms (Canonical forms)

- SOP and POS (Standard forms)

## THE DECIMAL NUMBER SYSTEM

- The decimal system is the base-10 system that we use every day.

- A number, say 6357, represented in the base-10 system consists of multiple ordered digits. (In other words, digits are normally combined together in groups to create larger numbers.)

- A digit is a single place that can hold numerical values between 0 and 9 (10 different values).

#### Let us start from an arbitrary decimal number

• For example, 6,357 has four digits.

- It is understood that in the number 6,357,

- the 7 is filling the "1s place,"

- while the 5 is filling the 10s place,

- the 3 is filling the 100s place

- and the 6 is filling the 1,000s place.

- So you could express 6,357 this way if you want to be explicit: (6 \* 1000) + (3 \* 100) + (5 \* 10) + (7 \* 1) = 6000 + 300 + 50 + 7

- = 6357

- What you can see from this expression is that each digit is a placeholder for the power of the index of that placeholder of base 10, starting from the least significant digit with 10 raised to the power of zero (i.e. counting from the rightmost digit).

- But why do we human beings use 10 based number system?

- The most commonly accepted explanation is that our base-10 number system was adopted by our ancestors most likely because we have 10 fingers.

- > Interestingly enough, maybe that is why digit in English also means a finger or toe.

## **BINARY NUMBER**

- Computers happen to operate using the base-2 number system, also known as the binary number system, just like the base-10 number system is known as the decimal number system to human beings

- Modern computers use binary number system, in which there are only zeros and ones. (Only two symbols)

- A "bit" to binary is similar a "digit" to a decimal information. (Again, the easiest way to understand bits is to compare them to something you know: digits.)

- A **bit** has a single binary value, either 0 or 1.

#### Binary vs. Decimal

- Binary is a base two **system** which works just like our **decimal system**.

- Considering the decimal number system, it has a set of values which range from 0 to 9.

- The binary number system is base 2 and therefore requires only two digits, 0 and 1.

## Bits

- The binary number system uses binary digits (bits) in place of decimal digits.

- A binary number is composed of only 0s and 1s, like this: 1011.

- How do you figure out what the value of the binary number 1011 is in decimal world?

$$0 = 0$$

$1 = 1$

$$2 = 10$$

$$\bar{3} = 11$$

$$5 = 10^{\circ}$$

$$b = []$$

$$7 = 111$$

$$8 = 1000$$

$$9 = 1001$$

$$10 = 1010$$

$$|| = |0|$$

$$12 = 1100$$

## **DECIMAL TO BINARY**

• Keep dividing by 2

**Ex 2** : 237<sub>10</sub>

| 237 / 2 = 118                                                                       | Remainder 1 |

|-------------------------------------------------------------------------------------|-------------|

| 118 / 2 = 59                                                                        | Remainder 0 |

| 59 / 2 = 29                                                                         | Remainder 1 |

| 29/2=14                                                                             | Remainder 1 |

| 14/2=7                                                                              | Remainder 0 |

| 7 / 2 = 3                                                                           | Remainder 1 |

|                                                                                     | Remainder 1 |

| 3 / 2 = 1 / 1 / 1 / 1 / 2 = 0 / 1 / 1 / 2 = 0 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / | Remainder 1 |

1 1 1 0 1 1 0 1

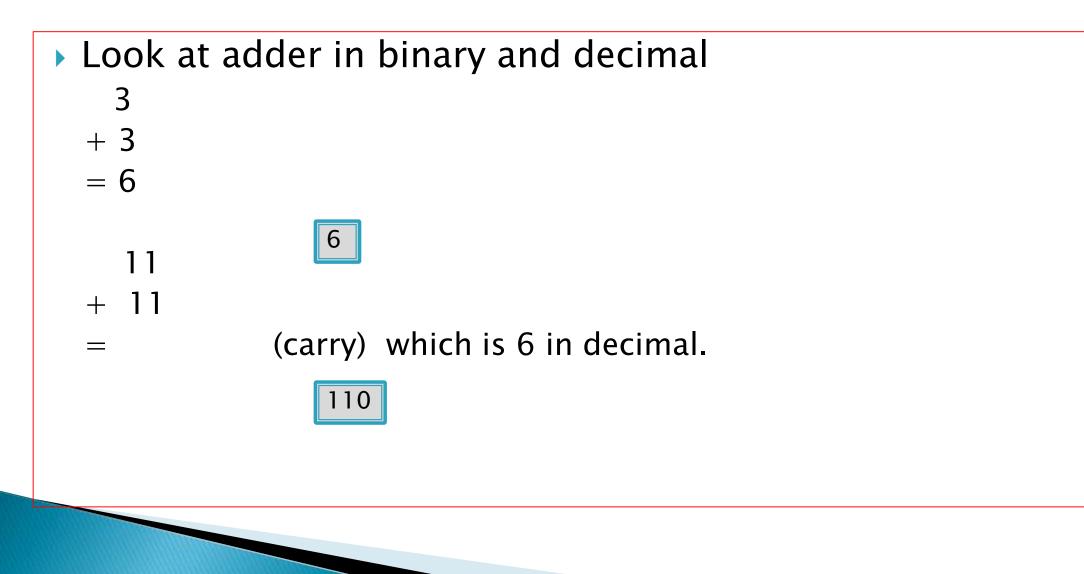

#### **Binary arithmetic operation**

## The Hexadecimal System

- Although not a problem internally, long binary number seems a problem to display in some situations. A common practice to solve this problem is to use hexadecimal to represent Binary numbers more compactly externally.

- The hexadecimal system is base 16. Therefore, it requires 16 different symbols. The values 0 through 9 are used, along with the letters A through F, which represent the decimal values 10 through 15.

0..9, A, B, C, D, E, F 0..9, 10, 11, 12,13, 14, 15

#### Hexadecimal <->binary

| binary | Hexadecimal |  |

|--------|-------------|--|

| 0000   | 0           |  |

| 0001   | 1           |  |

| 0010   | 2           |  |

| 0011   | 3           |  |

| 0100   | 4           |  |

| 0101   | 5           |  |

| 0110   | 6           |  |

| 0111   | 7           |  |

| 1000   | 8           |  |

| 1001   | 9           |  |

| 1010   | A           |  |

| 1011   | В           |  |

| 1100   | С           |  |

| 1101   | D           |  |

| 1110   | E           |  |

| 1111   | F           |  |

## THE OCTAL SYSTEM

- The Octal system is **base 8**. Therefore it requires 8 digits. The values 0 through 7 are used.

- Octal to hexadecimal conversion, or visa versa, is most easily performed by first converting to binary.

## **BINARY TO OCTAL**

A binary number is converted to octal by grouping of 3 bits

$1 \ 1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 1 - - - - - - - \rightarrow 655$

The binary, hexadecimal (hex) and octal system share one common feature – they are all based on powers of 2.

Each digit in the hex system is equivalent to a fourdigit binary number and each digit in the octal system is equivalent to a 3-digit binary number.

## MinTerms

- Consider a system of 3 input signals (variables) x, y, & z.

- A term which ANDs all input variables, either in the true or complement form, is called a minterm.

- > Thus, the considered 3-input system has 8 minterms, namely:

Thus, for example, is a = 000, where it is equal to 1.

- Accordingly, the minterm is referred to as m<sub>0</sub>.

- In general, minterms are designat  $\overline{x y z}$ , where i corresponds the input combination at which this minterm is equal to 1.

#### MinTerms

- For the 3-input system under consideration, the number of possible input combinations is 2<sup>3</sup>, or

8 This means that the system has a total of 8

- $m_0 = \overline{x} \ \overline{y} \ \overline{z} = 1$  IFF xyz = 000, otherwise it equals 0

- >  $m_1 = \overline{x yz} = 1$  IFF xyz = 001, otherwise it equals 0

- >  $m_2 = \overline{xyz} = 1$  IFF xyz = 010, otherwise it equals 0

- $m_3 = \overline{xyz} = 1$  IFF xyz = 011, otherwise it equals 0

- >  $m_4 = xyz = 1$  IFF xyz = 100, otherwise it equals 0

- $m_5 = x yz = 1$  IFF xyz = 101, otherwise it equals 0

- >  $m_6 = xyz = 1$  IFF xyz = 110, otherwise it equals 0

- >  $m_7 = xyz = 1$  IFF xyz = 111, otherwise it equals 0

## MinTerms

- In general, for n-input variables, the number of minterms = the total number of possible input combinations = 2<sup>n</sup>.

- A minterm = 0 at all input combinations except one where the minterm = 1.

- Example: What is the number of minterms for a function with 5 input variables?

- Number of minterms  $= 2^5 = 32$  minterms.

#### MaxTerms

- Consider a circuit of 3 input signals (variables) x, y, & z.

- A term which ORs all input variables, either in the true or complement form, is called a Maxterm.

- With 3-input variables, the system under consideration has a total of 8 Maxterms, namely:

- Ea (x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+y+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),(x+z),

- except for the combination xyz = 000, where it is equal to 0.

- Accordingly, the Maxterm (x + y + z) is referred to as  $M_0$ .

#### MaxTerms

In general, Maxterms are designated M<sub>i</sub>, where i corresponds to the input combination at which this Maxterm is equal to 0.

$M_0 = (x + y + z) = 0$  IFF xyz = 000, otherwise it equals 1 OSSIBLE

- >  $M_1 = (x + y + \overline{z}) = 0$  IFF xyz = 001, otherwise it equals 1 is that the

- >  $M_2 = (x + \overline{y} + z) = 0$  IFF xyz = 010, otherwise it equals 1 WS:

- >  $M_3 = (x + \overline{y} + \overline{z}) = 0$  IFF xyz = 011, otherwise it equals 1

- >  $M_4 = (\overline{x} + y + z) = 0$  IFF xyz = 100, otherwise it equals 1

- >  $M_5 = (\overline{x} + y + \overline{z}) = 0$  IFF xyz = 101, otherwise it equals 1

- $M_{\delta} = (\overline{x} + \overline{y} + z) = 0 \quad \text{IFF} \quad xyz = 110, \text{ otherwise it equals 1}$

- >  $M_7 = (\overline{x} + \overline{y} + \overline{z}) = 0$  IFF xyz = 111, otherwise it equals 1

#### MaxTerms

- For n-input variables, the number of Maxterms = the total number of possible input combinations = 2<sup>n</sup>.

- A Maxterm = 1 at all input combinations except one where the Maxterm = 0.

- Using De-Morgan's theorem, or truth tables, it can be easily shown that:

$M_i = m_i$   $\forall i = 0, 1, 2, ..., (2^n - 1)$

#### **Expressing Functions as a Sum of Minterms**

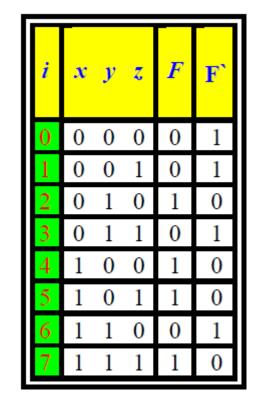

- Consider the function F defined by the shown truth table:

- Now let's rewrite the table, with few added columns.

- A column i indicating the input combination

- Four columns of minterms m<sub>2</sub>, m<sub>4</sub>, m<sub>5</sub> and m<sub>7</sub>

- One last column OR-ing the above minterms (m<sub>2</sub>+m<sub>4</sub>+m<sub>5</sub>+m<sub>7</sub>)

- From this table, we can clearly see that F =  $m_2+m_4+m_5+m_7$

| i | хy  | z | F | <i>m</i> <sub>2</sub> | m4 | M5 | <b>m</b> 7 | $m_2 + m_4 + m_5 + m_7$ |

|---|-----|---|---|-----------------------|----|----|------------|-------------------------|

| 0 | 0 0 | 0 | 0 | 0                     | 0  | 0  | 0          | 0                       |

| 1 | 0 0 | 1 | 0 | 0                     | 0  | 0  | 0          | 0                       |

| 2 | 01  | 0 | 1 | 1                     | 0  | 0  | 0          | 1                       |

| 3 | 01  | 1 | 0 | 0                     | 0  | 0  | 0          | 0                       |

| 4 | 10  | 0 | 1 | 0                     | 1  | 0  | 0          | 1                       |

| 5 | 10  | 1 | 1 | 0                     | 0  | 1  | 0          | 1                       |

| 6 | 1 1 | 0 | 0 | 0                     | 0  | 0  | 0          | 0                       |

| 7 | 11  | 1 | 1 | 0                     | 0  | 0  | 1          | 1                       |

#### **Expressing Functions as a Sum of Minterms**

- In general, Any function can be expressed by **OR-ing** all minterms (m<sub>i</sub>) corresponding to input combinations (i) at which the function has a value of 1.

- The resulting expression is commonly referred to as the **SUM of minterms** and is typically expressed as  $F = \Sigma(2, 4, 5, 7)$ , where  $\Sigma$  indicates **OR-ing** of the indicated minterms. Thus,  $F = \Sigma(2, 4, 5, 7) = (m2 + m4 + m5 + m7)$

#### Expressing Functions as a Sum of Minterms

- The truth table of F` shows that F` equals 1 at i = 0, 1, 3 and 6, then,

- $F = m_0 + m_1 + m_3 + m_6$ ,

- $F' = \Sigma(0, 1, 3, 6),$

- $F = \Sigma(2, 4, 5, 7)$

- The sum of minterms expression of F` contains all minterms that do not appear in the sum of minterms expression of F.

#### **Expressing Functions as a Product of Sums**

Using De-Morgan theorem on equation:

$\overline{F} = \overline{(m_2 + m_4 + m_5 + m_7)} = \overline{m_2}.\overline{m_4}.\overline{m_5}.\overline{m_7} = M_2.M_4.M_5.M_7$

This form is designated as the Product of Maxterms and is expressed using the Π symbol, which is used to designate product in regular algebra, but is used to designate AND-ing in Boolean algebra.

►

$$F' = \Pi (2, 4, 5, 7) = M_2 M_4 M_5 M_7$$

•  $F' = \Sigma(0 \ 1 \ 3 \ 6) = \Pi(2 \ 4 \ 5 \ 7)$

$F = \overline{F} = \overline{m_0 + m_1 + m_3 + m_6} = \overline{m_0} \cdot \overline{m_1} \cdot \overline{m_3} \cdot \overline{m_6} = M_0 \cdot M_1 \cdot M_3 \cdot M_6$

$\mathbf{F} = \sum (2, 4, 5, 7) = \prod (0, 1, 3, 6)$

$\mathbf{F} = \prod (2, 4, 5, 7) = \sum (0, 1, 3, 6)$

# Expressing Functions as Sum of Minterms or Product of Maxterms

- Any function can be expressed both as a sum of minterms (Σ mi) and as a product of maxterms (Π Mj).

- The product of maxterms expression (Π Mj) of F contains all maxterms Mj (∀ j ≠ i) that do not appear in the sum of minterms expression of F.

- The sum of minterms expression of F<sup>°</sup> contains all minterms that do not appear in the sum of minterms expression of F.

- This is true for all complementary functions. Thus, each of the 2<sup>n</sup> minterms will appear either in the sum of minterms expression of F or the sum of minterms expression of F<sup>t</sup> but not both.

# Expressing Functions as Sum of Minterms or Product of Maxterms

- The product of maxterms expression of F` contains all maxterms that do not appear in the product of maxterms expression of F.

- This is true for all complementary functions. Thus, each of the 2<sup>n</sup> maxterms will appear either in the product of maxterms expression of F or the product of maxterms expression of F<sup>\*</sup> but not both.

## Expressing Functions as Sum of Minterms or Product of Maxterms

- Example: Given that F (a, b, c, d) = Σ(0, 1, 2, 4, 5, 7), derive the product of maxterms expression of F and the two standard form expressions of F<sup>\*</sup>.

- Since the system has 4 input variables (a, b, c & d), the number of minterms and maxterms =  $2^4$  = 16

- F (a, b, c, d) =  $\Sigma(0, 1, 2, 4, 5, 7)$

- $F = \Pi (3, 6, 8, 9, 10, 11, 12, 13, 14, 15)$

- $F' = \Sigma (3, 6, 8, 9, 10, 11, 12, 13, 14, 15).$

- $F' = \Pi(0, 1, 2, 4, 5, 7)$

# Finding the Sum of Minterms from a Given Expression

- Let F(A,B,C) = A B + A' C, express F as a sum of minterms

- F(A,B,C) = A B (C+C') + A' C (B+B')

- = ABC + ABC' + A'BC + A'B'C

- =  $\Sigma(1, 3, 6, 7)$

- Short Cut Method:

- AB = 11 This gives us the input combinations 110 and 111 which correspond to m6 and m7

- A' C = 0 1 This gives us the input combinations 001 and 011 which correspond to m1 and m3

## **Operations on Functions**

- The AND operation on two functions corresponds to the intersection of the two sets of minterms of the functions

- The OR operation on two functions corresponds to the union of the two sets of minterms of the functions

- ► Example

- Let  $F(A,B,C)=\Sigma m(1, 3, 6, 7)$  and  $G(A,B,C)=\Sigma m(0,1, 2, 4, 6, 7)$

- $F . G = \Sigma m(1, 6, 7)$

- $F + G = \Sigma m(0,1, 2, 3, 4, 6, 7)$

- F'.G=?

- $F' = \Sigma m(0, 2, 4, 5)$

- $F . G = \Sigma m(0, 2, 4)$

## **Canonical Forms**

- The sum of minterms and the product of maxterms forms of Boolean expressions are known as canonical forms.

- Canonical form means that all equivalent functions will have a unique and equal representation.

- Two functions are equal if and only if they have the same sum of minterms and the same product of maxterms.

- Example:

- Are the functions F1 = a'b' + ac + bc' and F2 = a'c' + ab + b'c Equal?

- $F1 = a'b' + ac + bc' = \Sigma m(0, 1, 2, 5, 6, 7)$

- $\circ \ F2 = \ a' \ c' + a \ b + b' \ c = \Sigma m(0, \ 1, \ 2 \ , \ 5, \ 6, \ 7)$

- They are equal as they have the same set of **minterms.**

## **Standard Forms**

- A **product term** is a term with ANDed literals. Thus, AB, A'B, A'CD are all product terms.

- A minterm is a special case of a product term where all input variables appear in the product term either in the true or complement form.

- A sum term is a term with ORed literals. Thus, (A+B), (A'+B), (A'+C+D) are all sum terms.

- A maxterm is a special case of a sum term where all input variables, either in the true or complement form, are ORed together.

## **Standard Forms**

- Boolean functions can generally be expressed in the form of a Sum of Products (SOP) or in the form of a Product of Sums (POS).

- The sum of minterms form is a special case of the SOP form where all product terms are minterms.

- The product of maxterms form is a special case of the POS form where all sum terms are maxterms.

- The SOP and POS forms are Standard forms for representing Boolean functions.

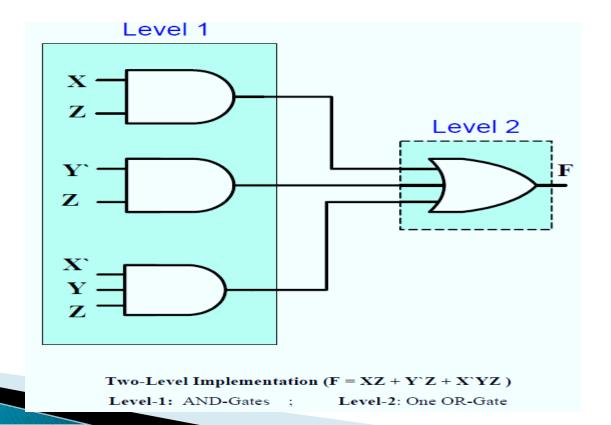

#### **Two-Level Implementations of Standard Forms**

#### Sum of Products Expressions (SOP):

- Any SOP expression can be implemented in 2-levels of gates.

- The first level consists of a number of AND gates which equals the number of product terms in the expression.

- Each AND gate implements one of the product terms in the expression.

- The second level consists of a SINGLE OR gate whose number of inputs equals the number of product terms in the expression.

**Two-Level Implementations of Standard Forms**

Example: Implement the following SOP function

F = XZ + Y`Z + X`YZ

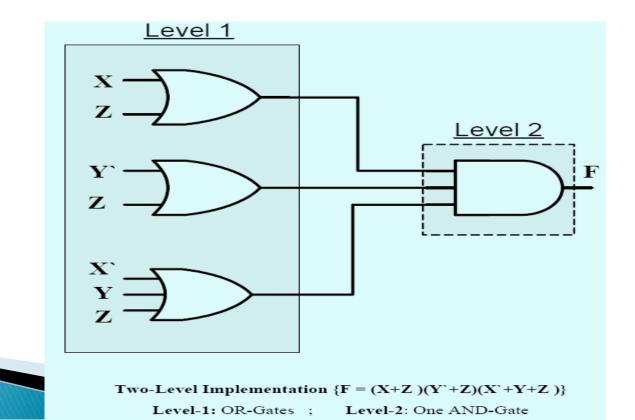

#### **Two-Level Implementations of Standard Forms**

#### **Product of Sums Expression (POS):**

- > Any POS expression can be implemented in 2-levels of gates.

- The first level consists of a number of OR gates which equals the number of sum terms in the expression.

- Each gate implements one of the sum terms in the expression.

- The second level consists of a SINGLE AND gate whose number of inputs equals the number of sum terms.

**Two-Level Implementations of Standard Forms**

Example: Implement the following POS function

F = (X+Z)(Y`+Z)(X`+Y+Z)

# **Boolean Algebra**

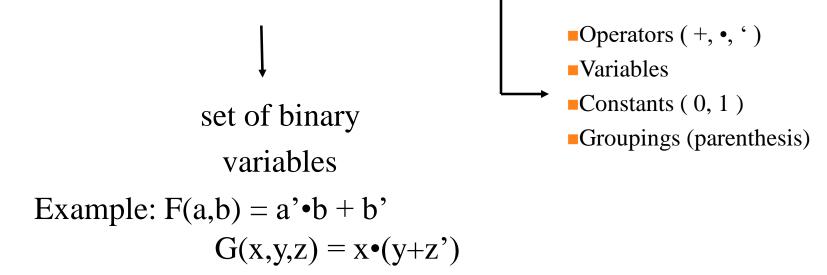

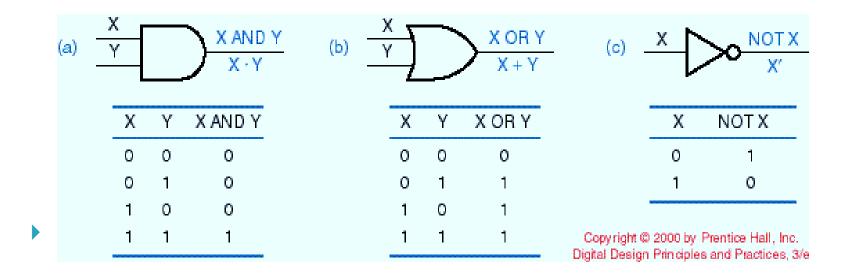

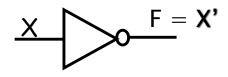

# **Binary Logic**

- Deals with binary variables that take 2 discrete values (0 and 1), and with logic operations

- Three basic logic operations:

- AND, OR, NOT

- Binary/logic variables are typically represented as letters: A,B,C,...,X,Y,Z

### **Binary Logic Function**

#### F(vars) = *expression*

## **Boolean Algebra**

- George Boole (1815-1864): "An investigation of the laws of thought"

- Terminology:

- *Literal:* A variable or its complement

- Product term: literals connected by •

- *Sum term:* literals connected by +

# Introduction

- ► 1854: Logical algebra was published by George Boole → known today as "Boolean Algebra"

- It's a convenient way and systematic way of expressing and analyzing the operation of logic circuits.

- I938: Claude Shannon was the first to apply Boole's work to the analysis and design of logic circuits.

#### **Boolean Operations & Expressions**

- ► **Variable** a symbol used to represent a logical quantity.

- **Complement** the inverse of a variable and is indicated by a bar over the variable.

- ▶ Literal a variable or the complement of a variable.

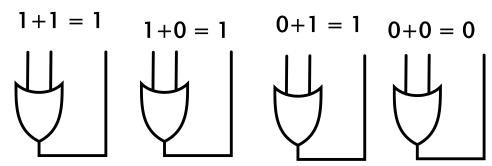

#### **Boolean Addition**

Boolean addition is equivalent to the OR operation

A sum term is produced by an OR operation with no AND ops involved.

i.e.  $A+B, A+\overline{B}, A+B+\overline{C}, \overline{A}+B+C+\overline{D}$

A **sum term** is equal to 1 when one or more of the literals in the term are 1.

A sum term is equal to 0 only if each of the literals is 0.

## **Boolean Multiplication**

Boolean multiplication is equivalent to the AND operation

#

A **product term** is produced by an AND operation with no OR ops involved.

i.e.

are U.

A **product term** is equal to 1 only if each of the literals in the term is 1.

A product term is equal to 0 when one or more of the literals

### Laws & Rules of Boolean Algebra

> The basic laws of Boolean algebra:

- The **commutative** laws

- The **associative** laws

- The **distributive** laws

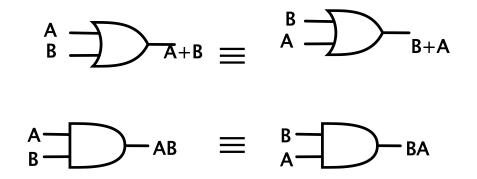

#### **Commutative Laws**

- The commutative law of addition for two variables is written as: A+B = B+A

- The commutative law of multiplication for two variables is written as: AB = BA

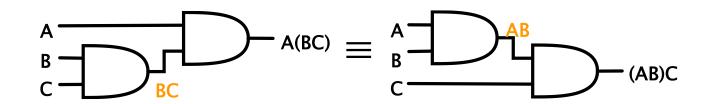

#### **Associative Laws**

• The associative law of addition for 3 variables is written as: A + (B+C) = (A+B)+C

• The associative law of sublication for  $3 \times 1$  bles is written as: A(BC) = (AB)C  $B \longrightarrow B+C$   $A+(B+C) \equiv B \longrightarrow C$ (A+B)+C

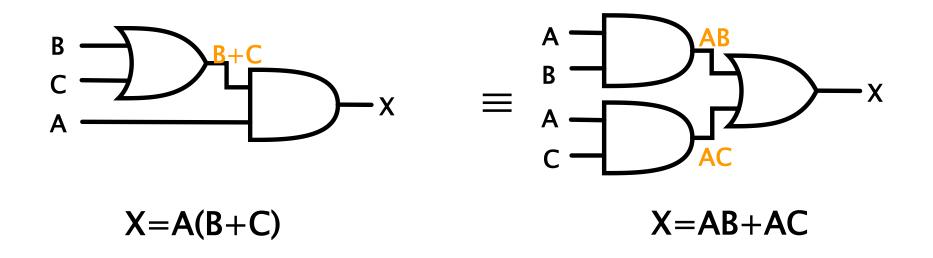

#### **Distributive Laws**

The distributive law is written for 3 variables as follows: A(B+C) = AB + AC

#### Rules of Boolean Algebra

| 1.A + 0 = A              | $7.A \bullet A = A$             |

|--------------------------|---------------------------------|

| 2.A + 1 = 1              | $8.A \bullet \overline{A} = 0$  |

| $3.A \bullet 0 = 0$      | $9.\overline{\overline{A}} = A$ |

| $4.A \bullet 1 = A$      | 10.A + AB = A                   |

| 5.A + A = A              | $11.A + \overline{A}B = A + B$  |

| $6.A + \overline{A} = 1$ | 12.(A+B)(A+C) = A + BC          |

A, B, and C can represent a single variable or a combination of variables.

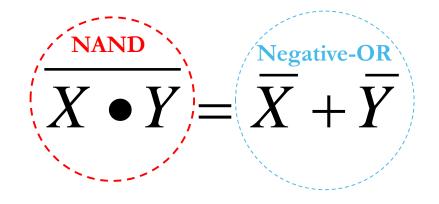

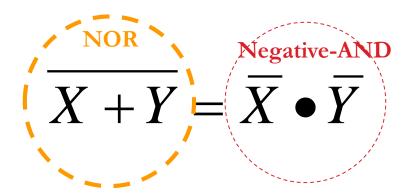

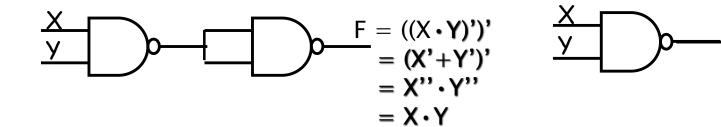

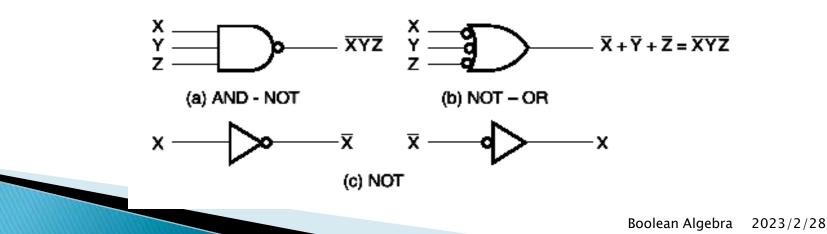

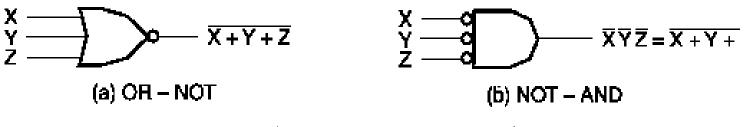

- > DeMorgan's theorems provide mathematical verification of:

- the equivalency of the NAND and negative-OR gates

- the equivalency of the NOR and negative-AND gates.

The complement of two or more ANDed variables is equivalent to the OR of the complements of the individual variables.

The complement of two or more ORed variables is equivalent to the AND of the complements of the individual variables.

• Apply DeMorgan's theorems to the expressions:

$\overline{X \bullet Y \bullet Z} \\

\overline{X + Y + Z} \\

\overline{\overline{X} + \overline{Y} + \overline{Z}} \\

\overline{\overline{W} \bullet \overline{X} \bullet \overline{Y} \bullet \overline{Z}}$

• Apply DeMorgan's theorems to the expressions:

$\overline{(A+B+C)D}$   $\overline{ABC+DEF}$   $\overline{A\overline{B}+\overline{C}D+EF}$   $\overline{\overline{A}\overline{B}+\overline{C}D+EF}$   $\overline{\overline{A+B\overline{C}}+D(\overline{E+\overline{F}})}$

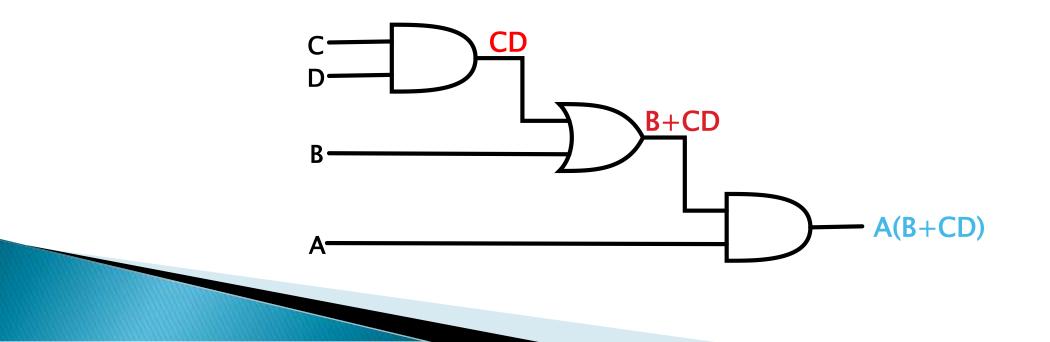

## Boolean Analysis of Logic Circuits

- Boolean algebra provides a concise way to express the operation of a logic circuit formed by a combination of logic gatese

- So that the output can be determined for various combinations of input values.

## **Boolean Expression for a Logic Circuit**

• To derive the Boolean expression for a given logic circuit, begin at the left-most inputs and work toward the final output, writing the expression for each gate.

- Once the Boolean expression for a given logic circuit has been determined, a truth table that shows the output for all possible values of the input variables can be developed.

- Let's take the previous circuit as the example:

A(B+CD)

• There are four variables, hence 16 (2<sup>4</sup>) combinations of values are possible.

Evaluating the expression

- To evaluate the expression A(B+CD), first find the values of the variables that make the expression equal to 1 (using the rules for Boolean add & mult).

- In this case, the expression equals 1 only if A=1 and B+CD=1 because  $A(B+CD) = 1 \cdot 1 = 1$

- Evaluating the expression (cont')

- Now, determine when B+CD term equals 1.

- The term *B*+*CD*=1 if either *B*=1 or *CD*=1 or if both *B* and *CD* equal 1 because

$$B+CD = 1+0 = 1$$

$B+CD = 0+1 = 1$

$B+CD = 1+1 = 1$

• The term CD=1 only if C=1 and D=1

- Evaluating the expression (cont')

- Summary:

- A(B+CD)=1

- When A=1 and B=1 regardless of the values of C and D

- When A=1 and C=1 and D=1 regardless of the value of B

- The expression A(B+CD)=0 for all other value combinations of the variables.

Putting the results in truth table format

A(B+CD)=1

When A=1 and B=1 regardless of the values of C and D

When A=1 and C=1 and D=1 regardless of the value of B

|   | OUTPUT |   |   |         |

|---|--------|---|---|---------|

| A | В      | С | D | A(B+CD) |

| 0 | 0      | 0 | 0 | 0       |

| 0 | 0      | 0 | 1 | 0       |

| 0 | 0      | 1 | 0 | 0       |

| 0 | 0      | 1 | 1 | 0       |

| 0 | 1      | 0 | 0 | 0       |

| 0 | 1      | 0 | 1 | 0       |

| 0 | 1      | 1 | 0 | 0       |

| 0 | 1      | 1 | 1 | 0       |

| 1 | 0      | 0 | 0 | 0       |

| 1 | 0      | 0 | 1 | 0       |

| 1 | 0      | 1 | 0 | 0       |

| 1 | 0      | 1 | 1 | 1       |

| 1 | 1      | 0 | 0 | 1       |

| 1 | 1      | 0 | 1 | 1       |

| 1 | 1      | 1 | 0 | 1       |

| 1 | 1      | 1 | 1 | 1       |

#### **Boolean Algebra Properties**

Let X: boolean variable, 0,1: constants

- 1. X + 0 = X -- Zero Axiom

- 2.  $X \bullet 1 = X$  -- Unit Axiom

- 3. X + 1 = 1 -- Unit Property

- 4.  $X \bullet 0 = 0$  -- Zero Property

#### **Boolean Algebra Properties**

Let X: boolean variable, 0,1: constants

- 5. X + X = X -- Idepotence

- 6.  $X \bullet X = X$  -- Idepotence

- 7. X + X' = 1 -- Complement

- 8.  $X \cdot X' = 0$  -- Complement

- 9. (X')' = X -- Involution

# Duality

- The dual of an expression is obtained by exchanging (• and +), and (1 and 0) in it, provided that the precedence of operations is not changed.

- Cannot exchange x with x'

- Example:

- Find H(x,y,z), the dual of F(x,y,z) = x'yz' + x'y'z

• H = (x'+y+z')(x'+y'+z)

# Duality

With respect to duality, Identities 1 - 8 have the following relationship:

1. X + 0 = X2.  $X \cdot 1 = X$  (dual of 1)3. X + 1 = 14.  $X \cdot 0 = 0$  (dual of 3)5. X + X = X6.  $X \cdot X = X$  (dual of 5)7. X + X' = 18.  $X \cdot X' = 0$  (dual of 8)

#### More Boolean Algebra Properties

Let X,Y, and Z: boolean variables

10. X + Y = Y + X11.  $X \cdot Y = Y \cdot X$  -- Commutative 12. X + (Y+Z) = (X+Y) + Z13.  $X \cdot (Y \cdot Z) = (X \cdot Y) \cdot Z$  -- Associative 14.  $X \cdot (Y+Z) = X \cdot Y + X \cdot Z$ 15.  $X + (Y \cdot Z) = (X+Y) \cdot (X+Z)$  -- Distributive 16.  $(X + Y)' = X' \cdot Y'$ 17.  $(X \cdot Y)' = X' + Y'$ -- DeMorgan's In general,  $(X_1 + X_2 + ... + X_n)' = X_1' \cdot X_2' \cdot ... \cdot X_n'$ , and  $(X_1 \cdot X_2 \cdot ... \cdot X_n)' = X_1' + X_2' + ... + X_n'$

#### **Absorption Property**

- 1.  $\mathbf{x} + \mathbf{x} \cdot \mathbf{y} = \mathbf{x}$

- 2.  $x \cdot (x+y) = x$  (dual)

- Proof:

$$x + x \bullet y = x \bullet 1 + x \bullet y$$

=  $x \bullet (1+y)$

=  $x \bullet 1$

=  $x$

QED (2 true by duality, why?)

#### **Power of Duality**

- 1.  $x + x \cdot y = x$  is true, so  $(x + x \cdot y)' = x'$

- 2.  $(x + x \cdot y)' = x' \cdot (x' + y')$

- 3.  $x' \cdot (x' + y') = x'$

- 4. Let X=x', Y=y'

- 5.  $X \bullet (X+Y) = X$ , which is the dual of  $x + x \bullet y = x$ .

- 6. The above process can be applied to any formula. So if a formula is valid, then its dual must also be valid.

- 7. Proving one formula also proves its dual.

#### **Consensus** Theorem

- 1. xy + x'z + yz = xy + x'z

- 2.  $(x+y)\bullet(x'+z)\bullet(y+z) = (x+y)\bullet(x'+z) -- (dual)$

- Proof:

- xy + x'z + yz = xy + x'z + (x+x')yz= xy + x'z + xyz + x'yz= (xy + xyz) + (x'z + x'zy)= xy + x'z

QED (2 true by duality).

# Truth Tables (revisited)

- Enumerates all possible combinations of variable values and the corresponding function value

- Truth tables for some arbitrary functions F<sub>1</sub>(x,y,z), F<sub>2</sub>(x,y,z), and F<sub>3</sub>(x,y,z) are shown to the right.

| × | У | Z | $F_1$ | $F_2$ | F₃ |

|---|---|---|-------|-------|----|

| 0 | 0 | 0 | 0     | 1     | 1  |

| 0 | 0 | 1 | 0     | 0     | 1  |

| 0 | 1 | 0 | 0     | 0     | 1  |

| 0 | 1 | 1 | 0     | 1     | 1  |

| 1 | 0 | 0 | 0     | 1     | 0  |

| 1 | 0 | 1 | 0     | 1     | 0  |

| 1 | 1 | 0 | 0     | 0     | 0  |

| 1 | 1 | 1 | 1     | 0     | 1  |

# **Truth Tables**

- > Truth table: a <u>unique</u> representation of a Boolean function

- If two functions have identical truth tables, the functions are equivalent (and vice-versa).

- > Truth tables can be used to prove equality theorems.

- However, the size of a truth table grows <u>exponentially</u> with the number of variables involved, hence unwieldy. This motivates the use of Boolean Algebra.

#### **Algebraic Manipulation**

- Boolean algebra is a useful tool for simplifying digital circuits.

- Why do it? Simpler can mean cheaper, smaller, faster.

- Example: Simplify F = x'yz + x'yz' + xz.

$$F = x'yz + x'yz' + xz$$

= x'y(z+z') + xz

= x'y•1 + xz

= x'y + xz

#### **Algebraic Manipulation**

- Example: Prove x'y'z' + x'yz' + xyz' = x'z' + yz'

- Proof:

$$x'y'z' + x'yz' + xyz'= x'y'z' + x'yz' + x'yz' + xyz'= x'z'(y'+y) + yz'(x'+x)= x'z' \cdot 1 + yz' \cdot 1= x'z' + yz'$$

QED.

#### **Complement of a Function**

- The complement of a function is derived by interchanging (• and +), and (1 and 0), and complementing each variable.

- Otherwise, interchange 1s to 0s in the truth table column showing F.

- The **complement** of a function IS NOT THE SAME as the *dual* of a function.

#### **Complementation: Example**

Find G(x,y,z), the complement of

F(x,y,z) = xy'z' + x'yz

•

$$G = F' = (xy'z' + x'yz)'$$

=  $(xy'z')' \cdot (x'yz)'$  DeMorgan

=  $(x'+y+z) \cdot (x+y'+z')$  DeMorgan again

Note: The complement of a function can also be derived by finding the function's *dual*, and then complementing all of the literals

## Truth Table notation for Minterms and Maxterms

- Minterms and Maxterms are easy to denote using a truth table.

- Example: Assume 3 variables x,y,z (order is fixed)

|   | X | У | Z | Minterm                | Maxterm                 |

|---|---|---|---|------------------------|-------------------------|

|   | 0 | 0 | 0 | $x'y'z' = m_0$         | $x+y+z = M_0$           |

|   | 0 | 0 | 1 | $x'y'z = m_1$          | x+y+z' = M <sub>1</sub> |

|   | 0 | 1 | 0 | x'yz' = m <sub>2</sub> | x+y'+z = M <sub>2</sub> |

| S | 0 | 1 | 1 | x'yz = m <sub>3</sub>  | x+y'+z'= M <sub>3</sub> |

|   | 1 | 0 | 0 | $xy'z' = m_4$          | $x'+y+z = M_4$          |

|   | 1 | 0 | 1 | xy'z = m <sub>5</sub>  | $x'+y+z' = M_5$         |

|   | 1 | 1 | 0 | $xyz' = m_6$           | $x'+y'+z = M_6$         |

|   | 1 | 1 | 1 | $xyz = m_7$            | $x'+y'+z' = M_7$        |

### UNIT II

- GATE LEVEL MINIMIZATION

- KARNAUGH MAP

- TABULAR MINIMIZATION METHOD

- COMBINATIONAL LOGIC

- BINARY ADDER –SUBTRACTER

- DECIMAL ADDER

- BINARY MMULTIPLIER

- MAGNITUDE COMPARATOR

- DECODER, ENCODER

- MULTIPLEXERS AND DEMULTIPLEXER

### UNIT II

#### • GATE LEVEL MINIMIZATION

- KARNAUGH MAP

- TABULAR MINIMIZATION METHOD

- POS AND SOP IMPLIMENTATION

- NAND & NOR IMPLIMENTATION NOR

- OTHER TWO LEVEL IMPLIMENTATION

- XOR IMPLIMENTATION

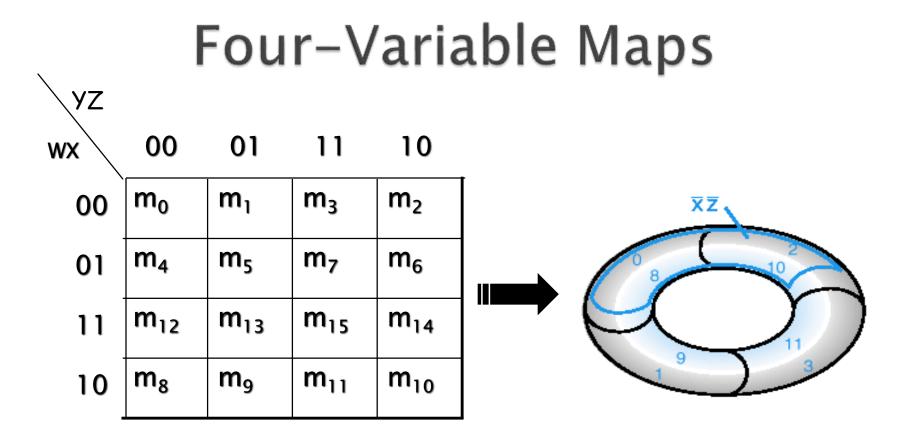

#### Karnaugh Maps

- Karnaugh maps (K-maps) are *graphical* representations of boolean functions.

- One *map cell* corresponds to a row in the truth table.

- Also, one map cell corresponds to a minterm or a maxterm in the boolean expression

- Multiple-cell areas of the map correspond to standard terms.

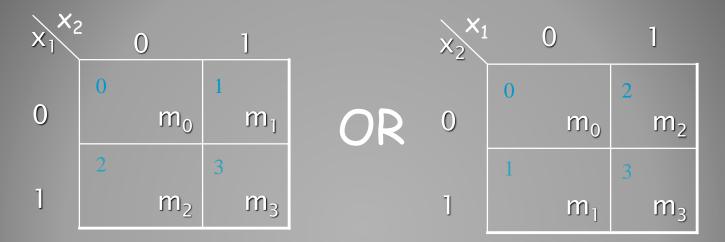

#### Two-Variable Map

NOTE: ordering of variables is IMPORTANT for  $f(x_1, x_2)$ ,  $x_1$  is the row,  $x_2$  is the column.

Cell **0** represents  $x_1'x_2'$ ; Cell **1** represents  $x_1'x_2$ ; etc. If a minterm is present in the function, then a 1 is placed in the corresponding cell.

#### Two-Variable Map (cont.)

- Any two adjacent cells in the map differ by ONLY one variable, which appears complemented in one cell and uncomplemented in the other.

- Example:

$m_0(=x_1, x_2)$  is adjacent to  $m_1(=x_1, x_2)$  and  $m_2(=x_1, x_2)$  but NOT  $m_3(=x_1, x_2)$

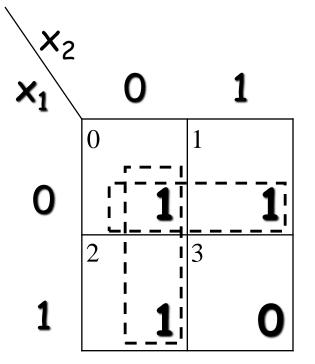

#### 2-Variable Map -- Example

- $f(x_1, x_2) = x_1' x_2' + x_1' x_2 + x_1 x_2'$ =  $m_0 + m_1 + m_2$ =  $x_1' + x_2'$

- 1s placed in K-map for specified minterms m<sub>0</sub>, m<sub>1</sub>, m<sub>2</sub>

- Grouping (ORing) of 1s allows simplification

- What (simpler) function is represented by each dashed rectangle?

•

$$x_1' = m_0 + m_1$$

•

$$x_2' = m_0 + m_2$$

▶ Note m<sub>0</sub> covered twice

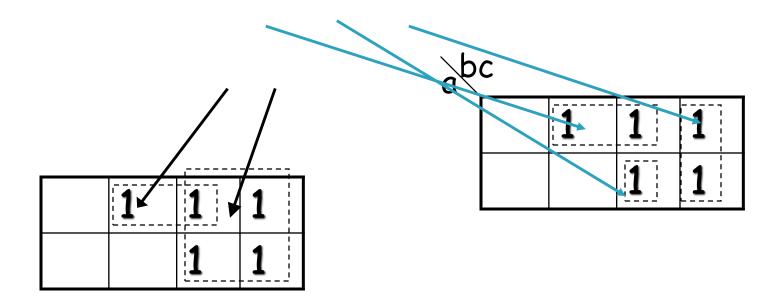

#### Minimization as SOP using K-map

- Enter 1s in the K-map for each product term in the function

- Group **adjacent** K-map cells containing 1s to obtain a product with fewer variables. Group size must be in power of 2 (2, 4, 8, ...)

- Handle "boundary wrap" for K-maps of 3 or more variables.

- Realize that answer may not be unique

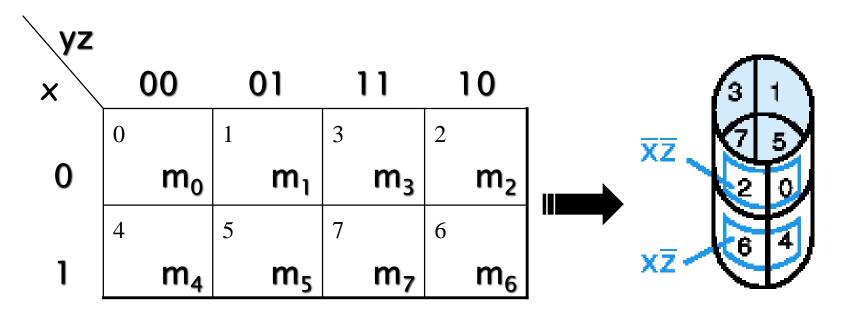

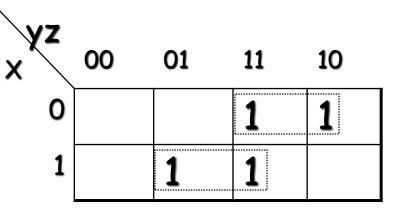

Three-Variable Map

-Note: variable ordering is (x,y,z); yz specifies column, x specifies row.

-Each cell is adjacent to *three* other cells (left or right or top or bottom or edge wrap)

#### Three-Variable Map (cont.)

, minterm The types of structures that are either minterms or are generated by repeated application of the minimization theorem on a three variable map are shown at right. Groups of 1, 2, 4, 8 are possible. group of 2 terms group of 4 terms

#### Simplification

- Enter minterms of the Boolean function into the map, then group terms

- Example: f(a,b,c) = a'c + abc + bc'

- Result: f(a,b,c) = a'c+b

#### More Examples

•

$$f_1(x, y, z) = \sum m(2,3,5,7)$$

•  $f_1(x, y, z) = x'y + xz$

•

$$f_2(x, y, z) = \sum m(0, 1, 2, 3, 6)$$

$$\mathbf{I}_2(\mathbf{x}, \mathbf{y}, \mathbf{z}) = \mathbf{x'} + \mathbf{y}\mathbf{z'}$$

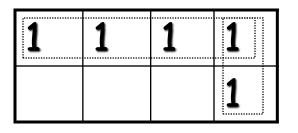

- Top cells are adjacent to bottom cells. Left-edge cells are adjacent to right-edge cells.

- Note variable ordering (WXYZ).

#### Four-variable Map Simplification

- One square represents a minterm of 4 literals.

- A rectangle of 2 adjacent squares represents a product term of 3 literals.

- A rectangle of 4 squares represents a product term of 2 literals.

- A rectangle of 8 squares represents a product term of 1 literal.

- A rectangle of 16 squares produces a function that is equal to logic 1.

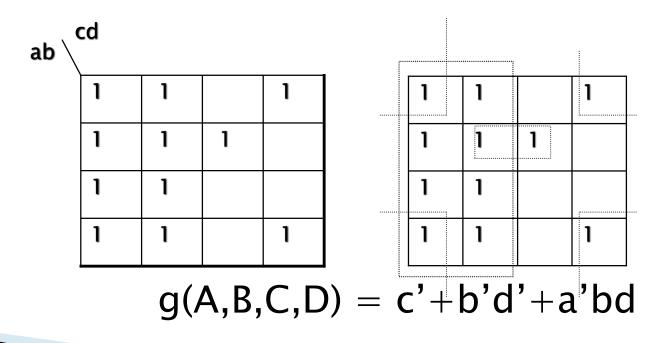

#### Example

- Simplify the following Boolean function  $(A,B,C,D) = \sum m(0,1,2,4,5,7,8,9,10,12,13).$

- First put the function g() into the map, and then group as many 1s as possible.

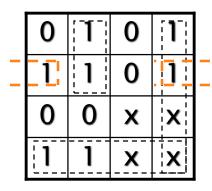

#### **Don't Care Conditions**

- There may be a combination of input values which

- will **never** occur

- if they do occur, the output is of no concern.

- The function value for such combinations is called a *don't care*.

- ▶ They are denoted with x or –. Each x may be arbitrarily assigned the value 0 or 1 in an implementation.

- Don't cares can be used to *further* simplify a function

#### Minimization using Don't Cares

- Treat don't cares as if they are 1s to generate PIs.

- Delete PI's that cover only don't care minterms.

- Treat the covering of remaining don't care minterms as optional in the selection process (*i.e.* they may be, but need not be, covered).

#### Example

- Simplify the function f(a,b,c,d) whose K-map is shown at the right.

- ▶ f = a'c'd+ab'+cd'+a'bc'

or

•

$$f = a'c'd+ab'+cd'+a'bd'$$

| ab | <b>I</b><br>00 | 01 | 11 | 10 |

|----|----------------|----|----|----|

| 00 | 0              | 1  | 0  | 1  |

| 01 | 1              | 1  | 0  | 1  |

| 11 | ο              | 0  | ×  | ×  |

| 10 | 1              | 1  | x  | ×  |

| 0          | 1  | 0 | ו |

|------------|----|---|---|

| <u> </u> ] | ٦, | 0 | 1 |

| 0          | 0  | Х | X |

| 1          | 1  | X | X |

#### Another Example

Simplify the function g(a,b,c,d) whose K-map is shown at right.

•

$$g = a'c' + ab$$

or

•

$$g = a'c' + b'd$$

| ab | d |   |   |   |

|----|---|---|---|---|

| 40 | x | 1 | 0 | 0 |

|    | 1 | X | 0 | x |

|    | 1 | × | x | 1 |

|    | 0 | X | X | 0 |

| X | 1 | 0 | 0 |

|---|---|---|---|

| 1 | X | 0 | X |

| 1 | × | X | 1 |

| 0 | X | X | 0 |

|   | X | 1 | 0 | 0 |   |

|---|---|---|---|---|---|

| - | 1 | X | 0 | X | - |

| _ | 1 | X | X | 1 | _ |

|   | 0 | X | X | 0 |   |

#### Algorithmic minimization

- What do we do for functions with more variables?

- > You can "code up" a minimizer (Computer-Aided Design, CAD)

- Quine-McCluskey algorithm

- Iterated consensus

- We won't discuss these techniques here

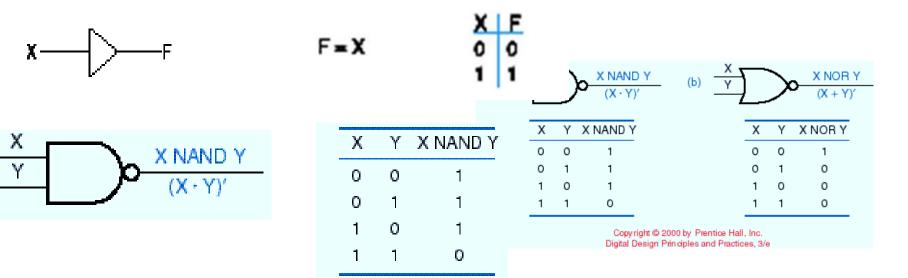

#### More Logic Gates

- NAND and NOR Gates

- NAND and NOR circuits

- Two-level Implementations

- Multilevel Implementations

- Exclusive-OR (XOR) Gates

- Odd Function

- Parity Generation and Checking

#### More Logic Gates

• We can construct any combinational circuit with AND, OR, and NOT gates

#### **BUFFER, NAND and NOR**

(a)

| Х | Y | X NOR Y |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 0       |

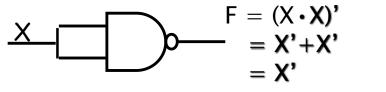

#### NAND Gate

- Known as a "Universal" gate because ANY digital circuit can be implemented with NAND gates alone.

- To prove the above, it suffices to show that AND, OR, and NOT can be implemented using NAND gates only.

#### **NAND Gate Emulation**

F X·Y

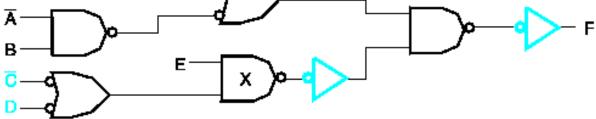

#### **NAND Circuits**

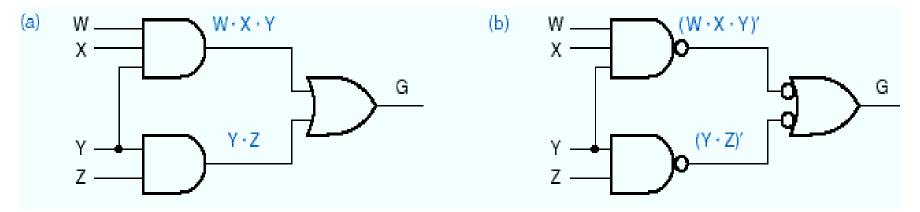

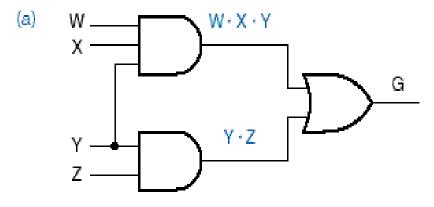

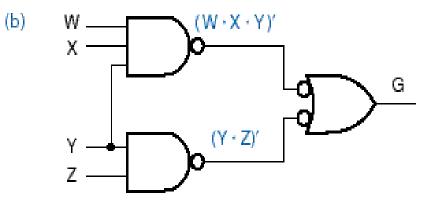

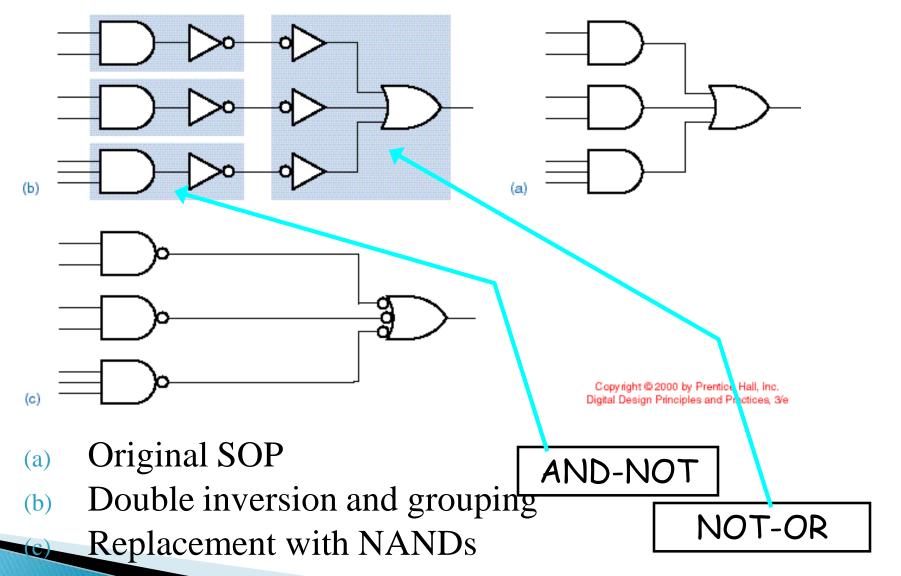

- To easily derive a NAND implementation of a boolean function:

- Find a simplified SOP

- SOP is an AND-OR circuit

- Change AND-OR circuit to a NAND circuit

- Use the alternative symbols below

## AND-OR (SOP) Emulation Using NANDs

#### Two-level implementations

- a) Original SOP

- b) Implementation with NANDs

#### AND-OR (SOP) Emulation Using NANDs (cont.)

Verify:

(a)

$$G = WXY + YZ$$

(b)

$$G = ((WXY)' \cdot (YZ)')'$$

=  $(WXY)'' + (YZ)'' = WXY + YZ$

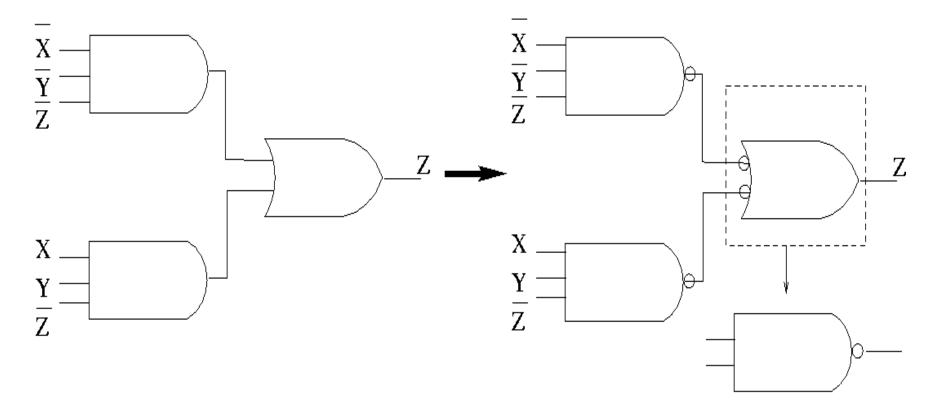

#### SOP with NAND

# Two-Level NAND Gate Implementation - Example

- $F(X,Y,Z) = \Sigma m(0,6)$

- 1. Express F in SOP form: F = X'Y'Z' + XYZ'

- 2. Obtain the AND-OR implementation for F.

- 3. Add bubbles and inverters to transform AND-OR to NAND-NAND gates.

Example (cont.)

### Two-level implementation with NANDs F = X'Y'Z' + XYZ'

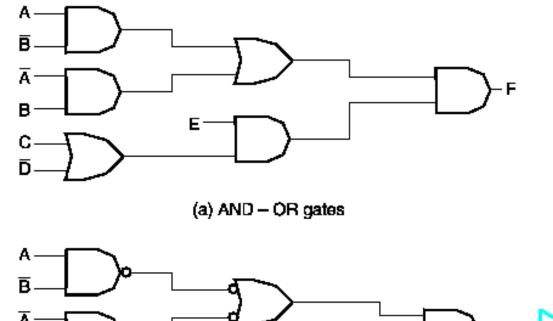

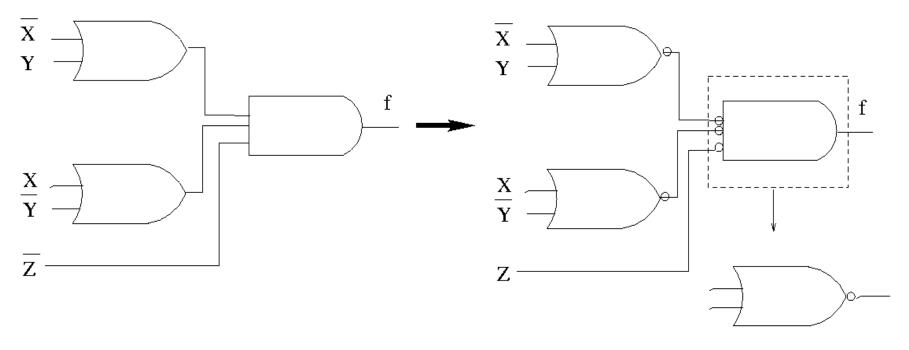

#### Multilevel NAND Circuits

Starting from a multilevel circuit:

- 1. Convert all AND gates to NAND gates with AND-NOT graphic symbols.

- 2. Convert all OR gates to NAND gates with NOT-OR graphic symbols.

- 3. Check all the bubbles in the diagram. For every bubble that is not counteracted by another bubble along the same line, insert a NOT gate or complement the input literal from its original appearance.

#### Yet Another Example!

(b) NAND gates

Fig. 2-32 Implementing  $F = (A \overline{B} + \overline{A}B)E(C + \overline{D})$

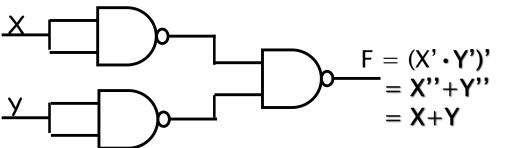

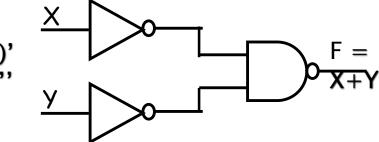

#### NOR Gate

- Also a "Universal" gate because ANY digital circuit can be implemented with NOR gates alone.

- > This can be similarly proven as with the NAND gate.

### **NOR Circuits**

- To easily derive a NOR implementation of a boolean function:

- Find a simplified POS

- POS is an OR-AND circuit

- Change OR-AND circuit to a NOR circuit

- Use the alternative symbols below

Fig. 2-34 Two Graphic Symbols for NOR Gate

# Two-Level NOR Gate Implementation - Example

$F(X,Y,Z) = \Sigma m(0,6)$ 1. Express F' in SOP form: a)F' =  $\Sigma m(1,2,3,4,5,7)$ = X'Y'Z + X'YZ' + X'YZ + XY'Z' + XY'Z + XYZ b)F' = XY' + X'Y + Z

- 2. Take the complement of F' to get F in the POS form: F = (F')' = (X'+Y)(X+Y')Z'

- 3. Obtain the OR-AND implementation for F.

- 4. Add bubbles and inverters to transform OR-AND implementation to NOR-NOR implementation.

#### Example (cont.)

#### Two-level implementation with NORs F = (F')' = (X'+Y)(X+Y')Z'

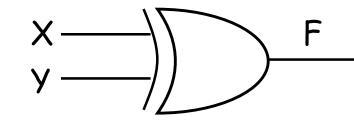

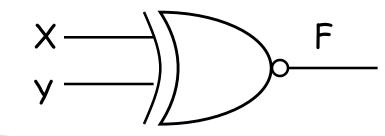

#### **XOR and XNOR**

XOR: "not-equal" gate

| Х | У | F = X⊕Y |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

| x | У | F = <del>X⊕</del> Y |  |  |

|---|---|---------------------|--|--|

| 0 | 0 | 1                   |  |  |

| 0 | 1 | 0                   |  |  |

| 1 | 0 | 0                   |  |  |

| 1 | 1 | 1                   |  |  |

XNOR: "equal" gate

#### Exclusive-OR (XOR) Function

- XOR (also  $\oplus$ ) : the "not-equal" function

- $XOR(X,Y) = X \oplus Y = X'Y + XY'$

- Identities:

- $X \oplus 0 = X$

- $X \oplus 1 = X'$

- $\circ \ X \oplus X = 0$

- $X \oplus X' = 1$

- Properties:

- $\circ \ X \oplus Y = Y \oplus X$

- $(X \oplus Y) \oplus W = X \oplus (Y \oplus W)$

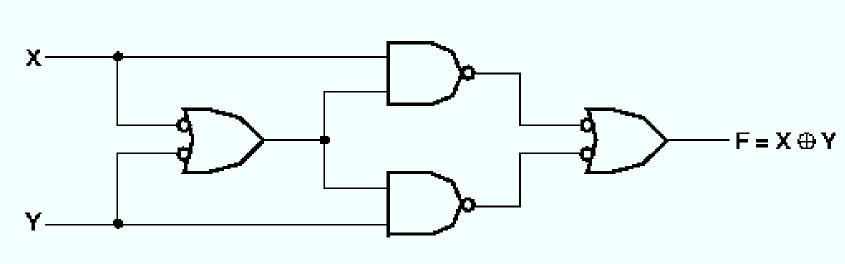

### **XOR function implementation**

- XOR(a,b) = ab' + a'b

- Straightforward: 5 gates

- 2 inverters, two 2-input ANDs, one 2-input OR

- 2 inverters & 3 2-input NANDs

- Nonstraightforward:

- 4 NAND gates

#### XOR circuit with 4 NANDs

Fig. 2-37 Exclusive-OR Constructed with NAND Gates

## UNIT III

- COMBINATIONAL LOGIC

- BINARY ADDER –SUBTRACTER

- DECIMAL ADDER

- BINARY MMULTIPLIER

- MAGNITUDE COMPARATOR

- DECODER, ENCODER

- MULTIPLEXERS AND DEMULTIPLEXER

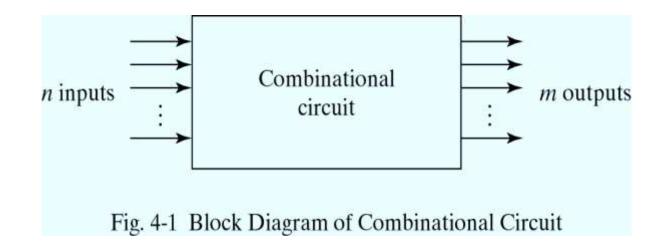

## Combinational Logic

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

#### Analysis procedure

- To obtain the output Boolean functions from a logic diagram, proceed as follows:

- 1. Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- 2. Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

- 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

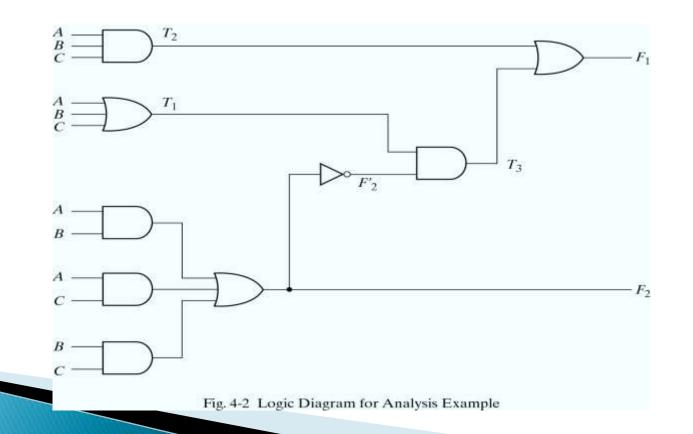

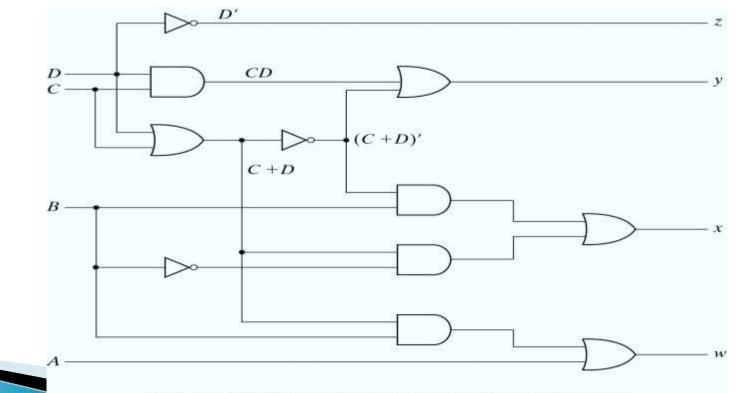

#### Example

$$\begin{split} F_2 &= AB + AC + BC; \ T_1 = A + B + C; \ T_2 = ABC; \ T_3 = F_2'T_1; \\ F_1 &= T_3 + T_2 \\ F_1 &= T_3 + T_2 = F_2'T_1 + ABC = A'BC' + A'B'C + AB'C' + ABC \end{split}$$

#### Derive truth table from logic diagram

• We can derive the truth table in Table 4-1 by using the circuit of Fig.4-2.

| Α | В | С | F <sub>2</sub> | <b>F</b> '2 | T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | F <sub>1</sub> |

|---|---|---|----------------|-------------|----------------|----------------|----------------|----------------|

| 0 | 0 | 0 | 0              | 1           | 0              | 0              | 0              | 0              |

| 0 | 0 | 1 | 0              | 1           | 1              | 0              | 1              | 1              |

| 0 | 1 | 0 | 0              | 1           | 1              | 0              | 1              | 1              |

| 0 | 1 | 1 | 1              | 0           | 1              | 0              | 0              | 0              |

| 1 | 0 | 0 | 0              | 1           | 1              | 0              | 1              | 1              |

| 1 | 0 | 1 | 1              | 0           | 1              | 0              | 0              | 0              |

| 1 | 1 | 0 | 1              | 0           | 1              | 0              | 0              | 0              |

| 1 | 1 | 1 | 1              | 0           | 1              | 1              | 0              | 1              |

#### Design procedure

1. Table4-2 is a Code-Conversion example, first, we can list the relation of the BCD and Excess-3 codes in the truth table.

|   | Input | BCD |   | Out | put Exe | cess-3 ( | Code |

|---|-------|-----|---|-----|---------|----------|------|

| A | В     | с   | D | w   | x       | y        | z    |

| 0 | 0     | 0   | 0 | 0   | 0       | 1        | 1    |

| 0 | 0     | 0   | 1 | 0   | 1       | 0        | 0    |

| 0 | 0     | 1   | 0 | 0   |         | 0        | 1    |

| 0 | 0     | 1   |   | 0   | 1       | 1        | 0    |

| 0 | 1     | 0   | 0 | 0   | 1       | 1        | 1    |

| 0 | 1     | 0   | 1 | 1   | 0       | 0        | 0    |

| 0 | 1     | 1   | 0 | 1   | 0       | 0        | 1    |

| 0 | 1     | 1   | 1 | 1   | 0       | 1        | 0    |

| 1 | 0     | 0   | 0 | 1   | 0       | 1        | 1    |

| 1 | 0     | 0   | 1 | 1   | 1       | 0        | 0    |

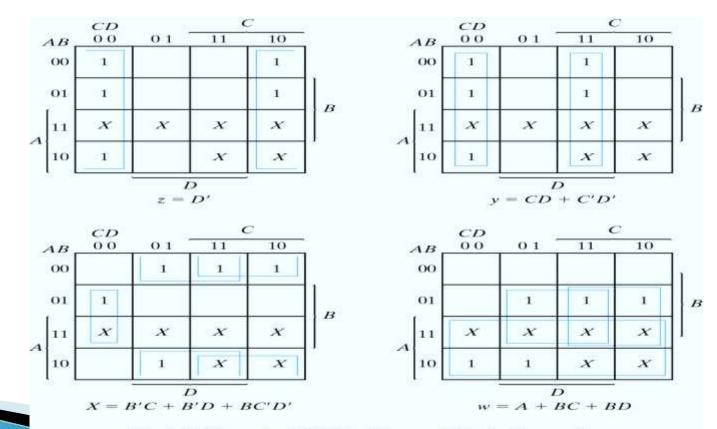

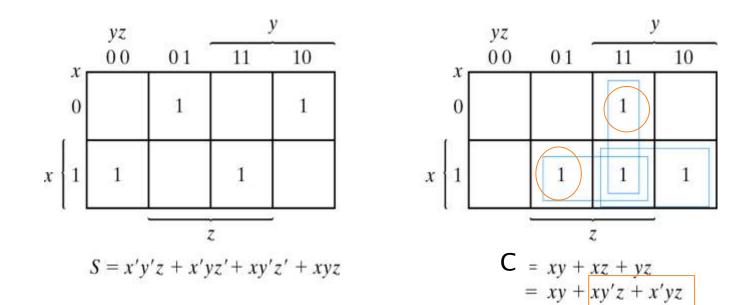

#### Karnaugh map

2. For each symbol of the Excess-3 code, we use 1's to draw the map for simplifying Boolean function.

Fig. 4-3 Maps for BCD to Excess-3 Code Converter

#### **Circuit implementation**

$$z = D';$$

$y = CD + C'D' = CD + (C + D)'$

$x = B'C + B'D + BC'D' = B'(C + D) + B(C + D)'$

$w = A + BC + BD = A + B(C + D)$

#### **Binary Adder-Subtractor**

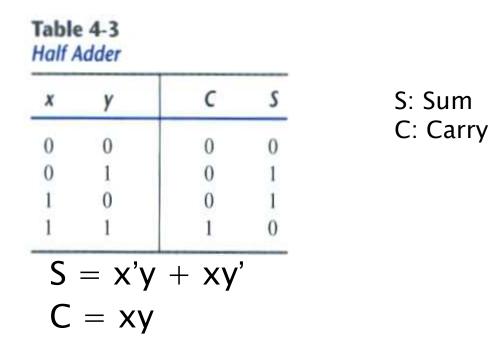

- A combinational circuit that performs the addition of two bits is called a half adder.

- The truth table for the half adder is listed below:

#### Implementation of Half-Adder

Fig. 4-5 Implementation of Half-Adder

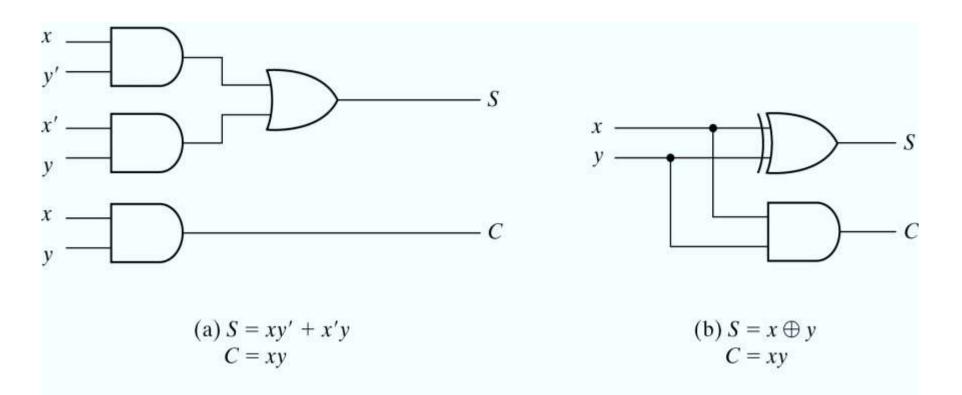

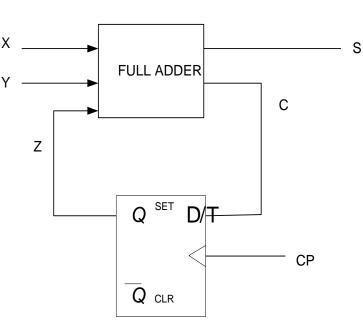

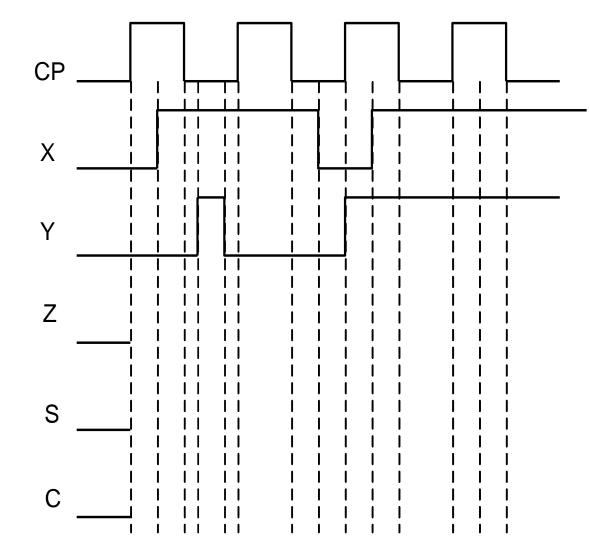

#### Full-Adder

One that performs the addition of three bits(two significant bits and a previous carry) is a full adder.

Table 4-4 Full Adder

| x | Y | z | С | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

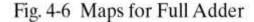

#### Simplified Expressions

S = x'y'z + x'yz' + xy'z' + xyzC = xy + xz + yz

#### Full adder implemented in SOP

Fig. 4-7 Implementation of Full Adder in Sum of Products

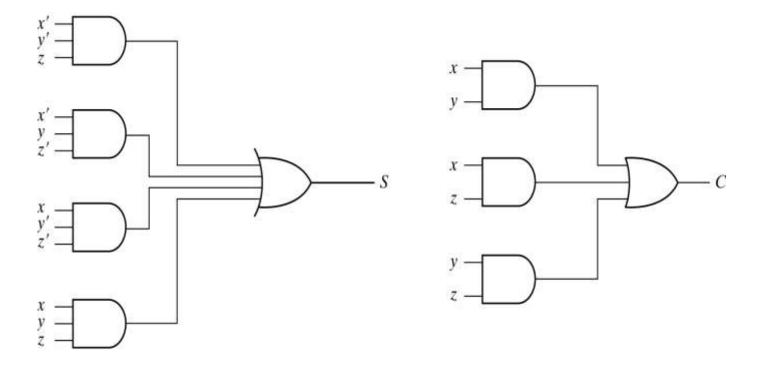

#### Another implementation

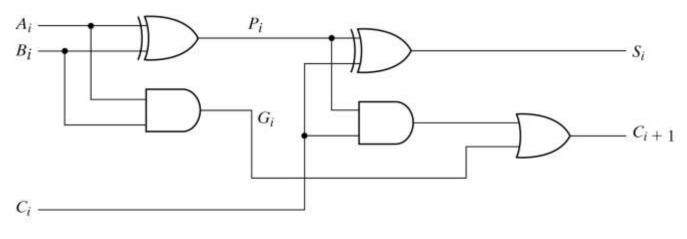

Full-adder can also implemented with two half adders and one OR gate (Carry Look-Ahead adder).

$$S = z \oplus (x \oplus y)$$

= z'(xy' + x'y) + z(xy' + x'y)'

= xy'z' + x'yz' + xyz + x'y'z

C = z(xy' + x'y) + xy = xy'z + x'yz + xy'z

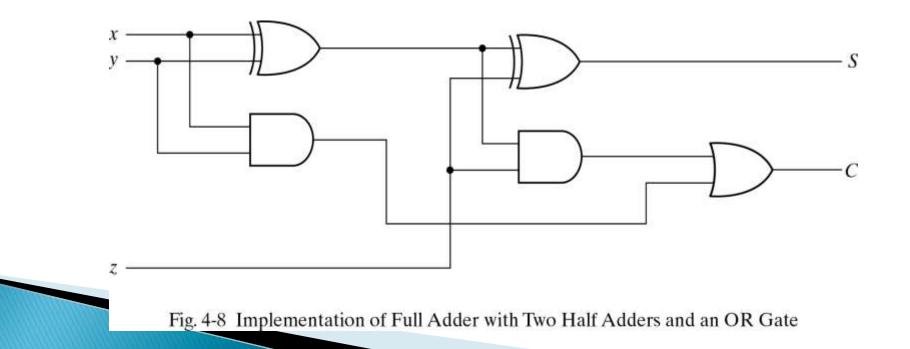

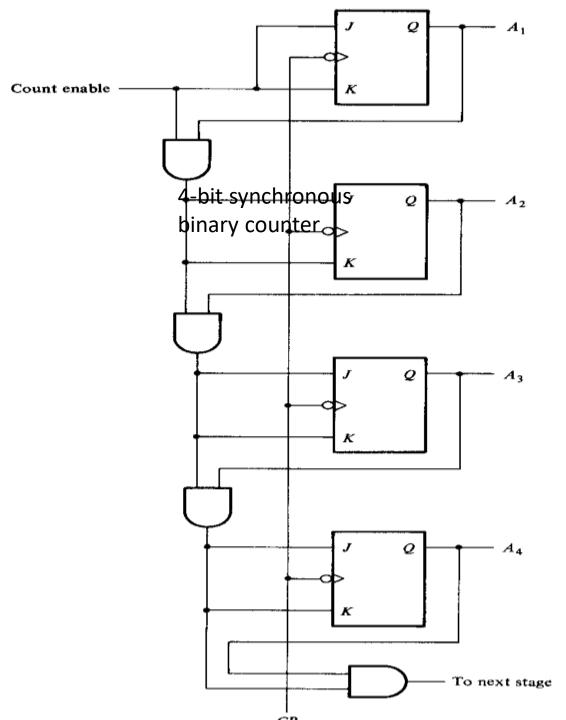

#### **Binary adder**

This is also called Ripple Carry Adder ,because of the construction with full adders are connected in cascade.

| Subscript i: | 3 | 2 | 1 | 0 |           |

|--------------|---|---|---|---|-----------|

| Input carry  | 0 | 1 | 1 | 0 | $C_i$     |

| Augend       | 1 | 0 | 1 | 1 | $A_i$     |

| Addend       | 0 | 0 | 1 | 1 | $B_i$     |

| Sum          | 1 | 1 | 1 | 0 | $S_i$     |

| Output carry | 0 | 0 | 1 | 1 | $C_{i+1}$ |

### **Carry Propagation**

- Fig.4-9 causes a unstable factor on carry bit, and produces a longest propagation delay.

- The signal from C<sub>i</sub> to the output carry C<sub>i+1</sub>, propagates through an AND and OR gates, so, for an n-bit RCA, there are 2n gate levels for the carry to propagate from input to output.

### **Carry Propagation**

- Because the propagation delay will affect the output signals on different time, so the signals are given enough time to get the precise and stable outputs.

- The most widely used technique employs the principle of carry look-ahead to improve the speed of the algorithm.

Fig. 4-10 Full Adder with P and G Shown

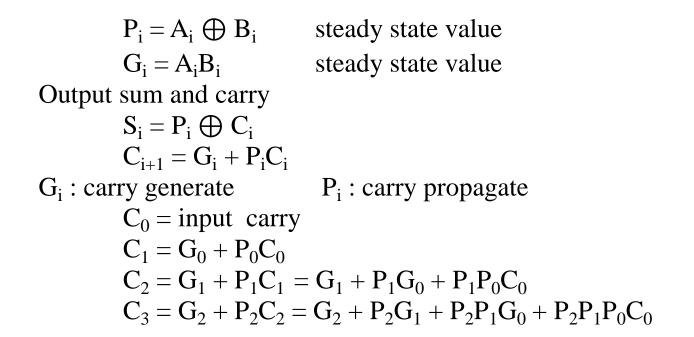

#### **Boolean functions**

C<sub>3</sub> does not have to wait for C<sub>2</sub> and C<sub>1</sub> to propagate.

#### Logic diagram of carry look-ahead generator

$\triangleright$  C<sub>3</sub> is propagated at the same time as C<sub>2</sub> and C<sub>1</sub>.

136

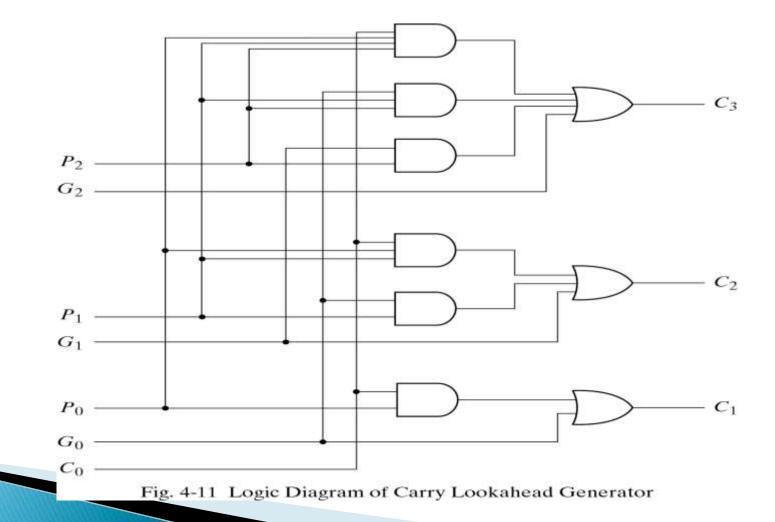

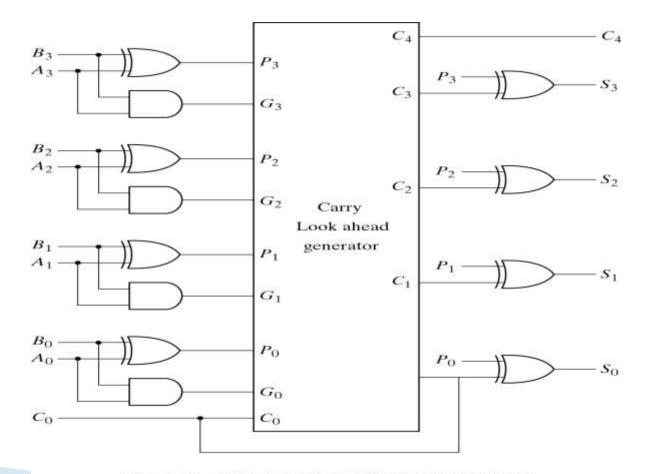

#### 4-bit adder with carry lookahead

Delay time of n-bit CLAA = XOR + (AND + OR) + XOR

Fig. 4-12 4-Bit Adder with Carry Lookahead

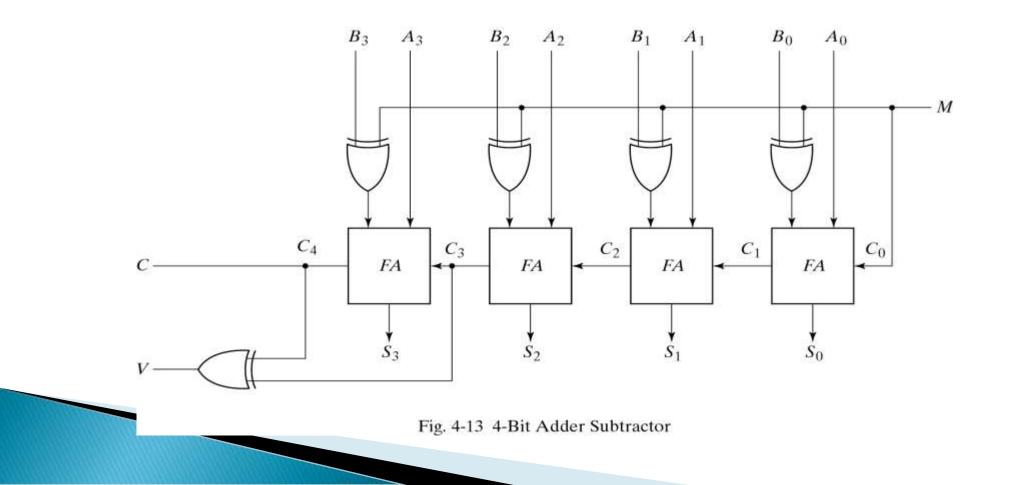

#### **Binary subtractor**

$M = 1 \rightarrow subtractor$ ;  $M = 0 \rightarrow adder$

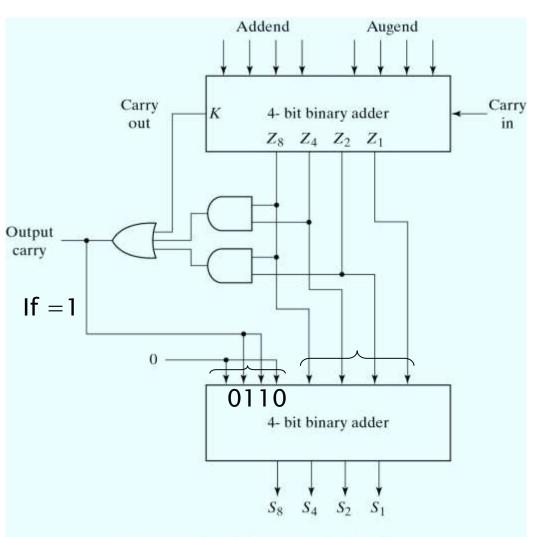

#### Decimal adder

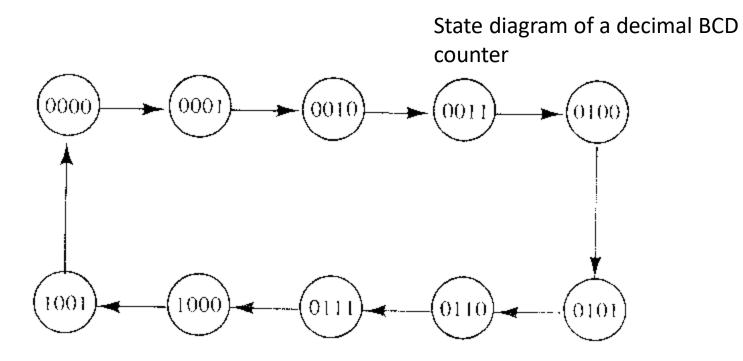

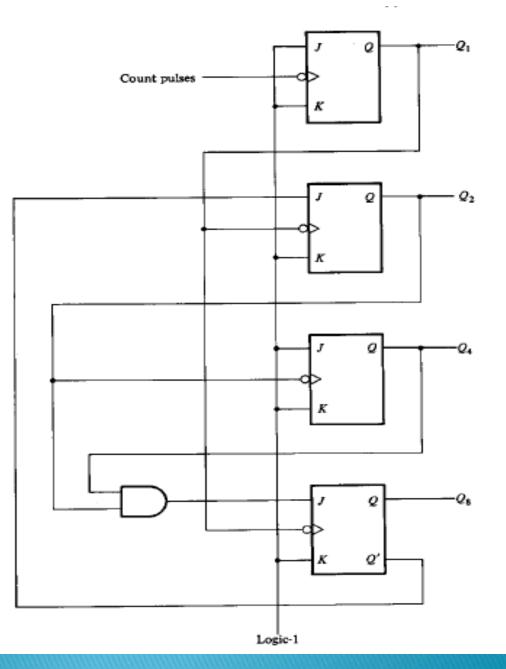

#### BCD adder can't exceed 9 on each input digit. K is the carry.

|   | Bir            | Binary Sum BCD Sum |                |                |   |                | BCD Sum    |    |                       |    |  |

|---|----------------|--------------------|----------------|----------------|---|----------------|------------|----|-----------------------|----|--|

| к | Z <sub>8</sub> | Z4                 | Z <sub>2</sub> | Z <sub>1</sub> | С | S <sub>8</sub> | <b>S</b> 4 | Sz | <i>S</i> <sub>1</sub> |    |  |

| 0 | 0              | 0                  | 0              | 0              | 0 | 0              | 0          | 0  | 0                     | 0  |  |

| 0 | 0              | 0                  | 0              | 1              | 0 | 0              | 0          | 0  | 1                     | 1  |  |

| 0 | 0              | 0                  | 1              | 0              | 0 | 0              | 0          | 1  | 0                     | 2  |  |

| 0 | 0              | 0                  | 1              | 1              | 0 | 0              | 0          | 1  | 1                     | 3  |  |

| 0 | 0              | 1                  | 0              | 0              | 0 | 0              | 1          | 0  | 0                     | 4  |  |

| 0 | 0              | 1                  | 0              | 1              | 0 | 0              | 1          | 0  | 1                     | 5  |  |

| 0 | 0              | 1                  | 1              | 0              | 0 | 0              | 1          | 1  | 0                     | 6  |  |

| 0 | 0              | 1                  | 1              | 1              | 0 | 0              | 1          | 1  | 1                     | 7  |  |

| 0 | 1              | 0                  | 0              | 0              | 0 | 1              | 0          | 0  | 0                     | 8  |  |

| 0 | 1              | 0                  | 0              | 1              | 0 | 1              | 0          | 0  | 1                     | 9  |  |

| 0 | 1              | 0                  | 1              | 0              | 1 | 0              | 0          | 0  | 0                     | 10 |  |

| 0 | 1              | 0                  | 1              | 1              | 1 | 0              | 0          | 0  | 1                     | 11 |  |

| 0 | 1              | 1                  | 0              | 0              | 1 | 0              | 0          | 1  | 0                     | 12 |  |

| 0 | 1              | 1                  | 0              | 1              | 1 | 0              | 0          | 1  | 1                     | 13 |  |

| 0 | 1              | 1                  | 1              | 0              | 1 | 0              | 1          | 0  | 0                     | 14 |  |

| 0 | 1              | 1                  | 1              | 1              | 1 | 0              | 1          | 0  | 1                     | 15 |  |

| 1 | 0              | 0                  | 0              | 0              | 1 | 0              | 1          | 1  | 0                     | 16 |  |

| 1 | 0              | 0                  | 0              | 1              | 1 | 0              | 1          | 1  | 1                     | 17 |  |

| 1 | 0              | 0                  | 1              | 0              | 1 | 1              | 0          | 0  | 0                     | 18 |  |

| 1 | 0              | 0                  | 1              | 1              | 1 | 1              | 0          | 0  | 1                     | 19 |  |

#### Table 4-5 Derivation of BCD Adder

#### Rules of BCD adder

- When the binary sum is greater than 1001, we obtain a non-valid BCD representation.

- The addition of binary 6(0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

- To distinguish them from binary 1000 and 1001, which also have a 1 in position Z<sub>8</sub>, we specify further that either Z<sub>4</sub> or Z<sub>2</sub> must have a 1.

$\mathbf{C} = \mathbf{K} + \mathbf{Z}_8 \mathbf{Z}_4 + \mathbf{Z}_8 \mathbf{Z}_2$

#### Implementation of BCD adder

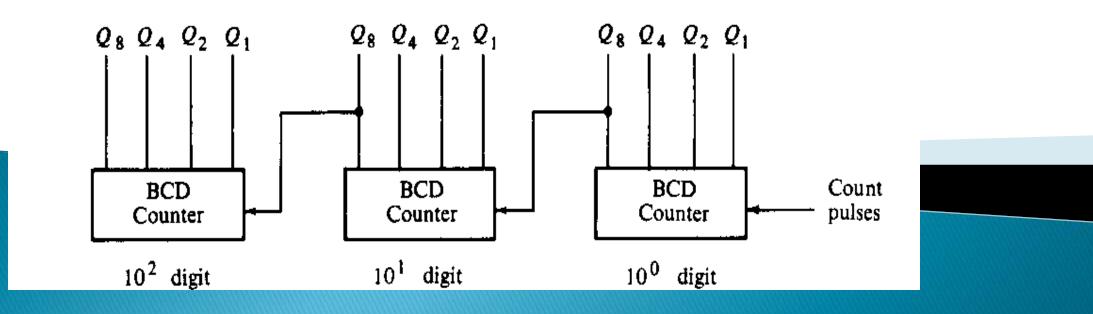

- A decimal parallel adder that adds n decimal digits needs n BCD adder stages.

- The output carry from one stage must be connected to the input carry of the next higher-order stage.

Fig. 4-14 Block Diagram of a BCD Adder

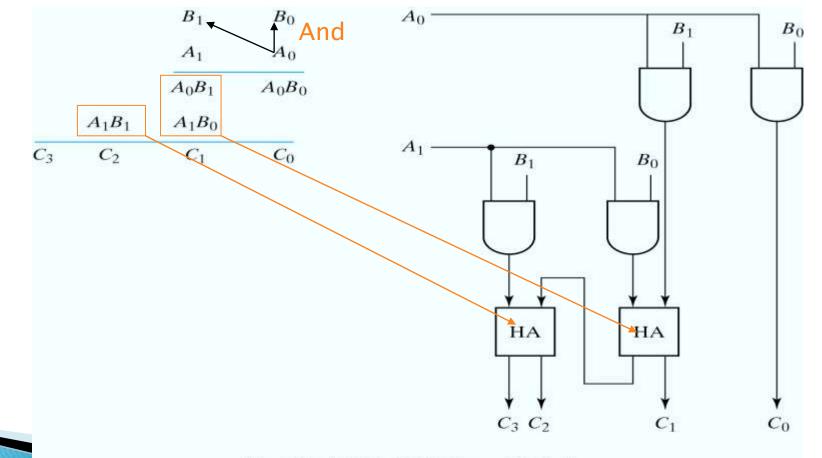

#### **Binary multiplier**

Usually there are more bits in the partial products and it is necessary to use full adders to produce the sum of the partial products.

Fig. 4-15 2-Bit by 2-Bit Binary Multiplier

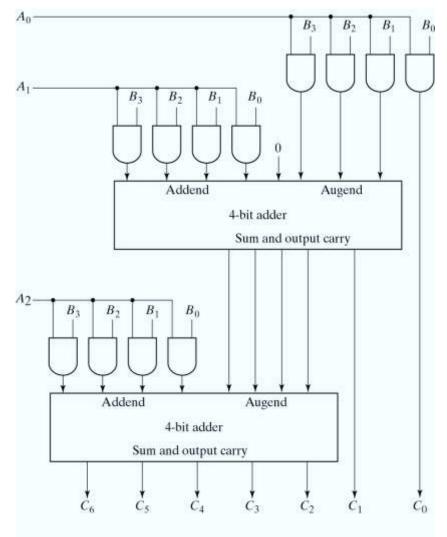

## 4-bit by 3-bit binary multiplier

- For J multiplier bits and K multiplicand bits we need (J X K)

AND gates and (J - 1) K-bit adders to produce a product of J+K bits.

- K=4 and J=3, we need 12 AND gates and two 4-bit adders.

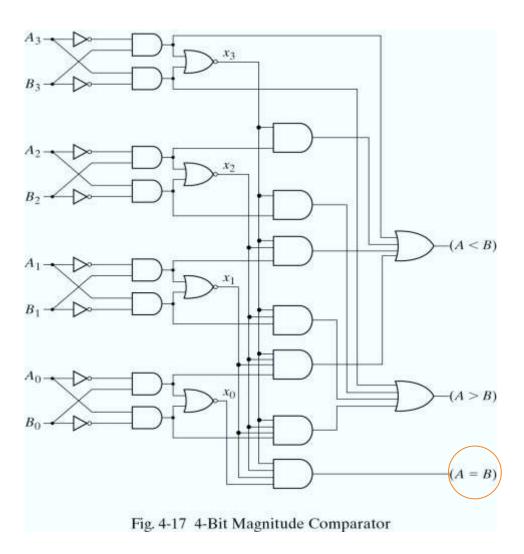

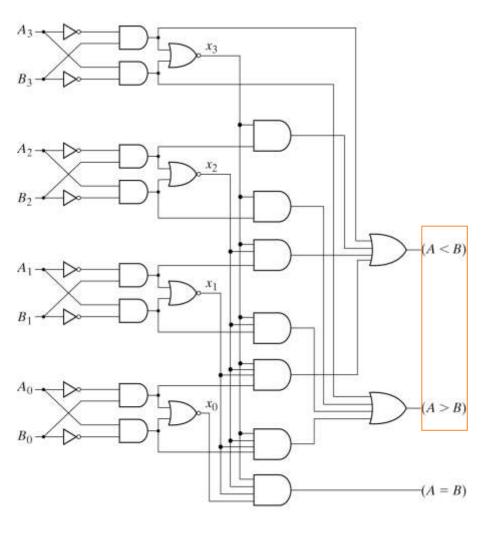

#### Magnitude comparator

The equality relation of each pair of bits can be expressed logically with an exclusive-NOR function as:

$$A = A_3 A_2 A_1 A_0$$

;  $B = B_3 B_2 B_1 B_0$

$x_i = A_i B_i + A_i' B_i'$  for i = 0, 1, 2, 3

$(\mathbf{A} = \mathbf{B}) = \mathbf{x}_3 \mathbf{x}_2 \mathbf{x}_1 \mathbf{x}_0$

# Magnitude comparator

- We inspect the relative magnitudes of pairs of MSB. If equal, we compare the next lower significant pair of digits until a pair of unequal digits is reached.

- If the corresponding digit of A is 1 and that of B is 0, we conclude that A>B.

$$(A>B)=$$

$$A_{3}B'_{3}+x_{3}A_{2}B'_{2}+x_{3}x_{2}A_{1}B'_{1}+x_{3}x_{2}x_{1}A_{0}B$$

$$i_{0}$$

$$(A

$$A'_{3}B_{3}+x_{3}A'_{2}B_{2}+x_{3}x_{2}A'_{1}B_{1}+x_{3}x_{2}x_{1}A'_{0}B$$$$

Fig. 4-17 4-Bit Magnitude Comparator

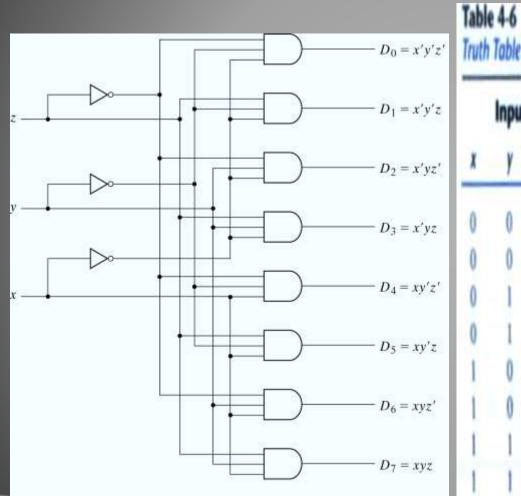

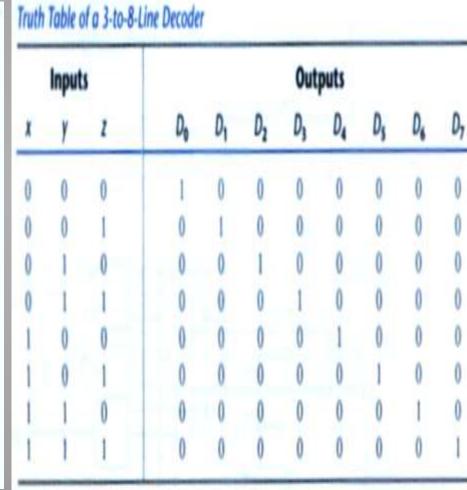

# Decoders

- The decoder is called n-to-m-line decoder, where  $m \le 2^n$ .

- the decoder is also used in conjunction with other code converters such as a BCD-toseven\_segment decoder.

- 3-to-8 line decoder: For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

#### Implementation and truth table

Fig. 4-18 3-to-8-Line Decoder

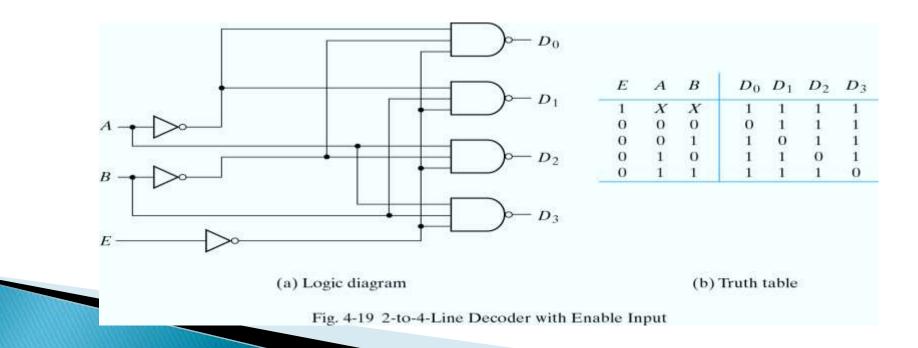

# Decoder with enable input

- Some decoders are constructed with NAND gates, it becomes more economical to generate the decoder minterms in their complemented form.

- As indicated by the truth table , only one output can be equal to 0 at any given time, all other outputs are equal to 1.

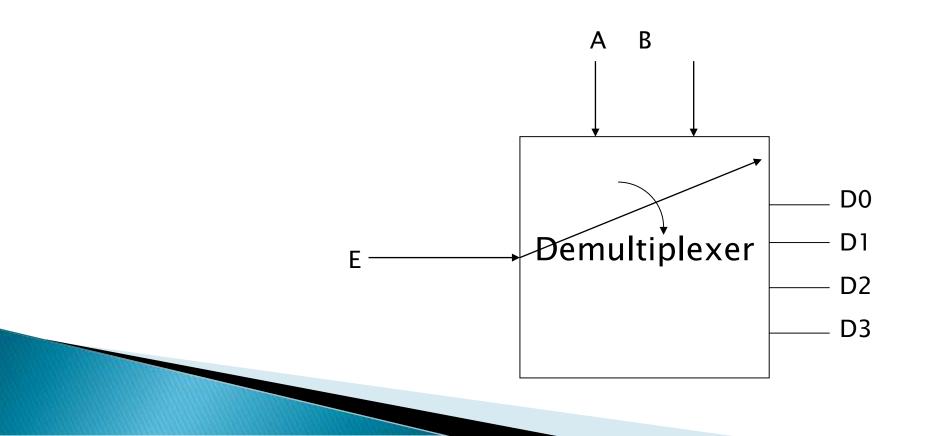

# Demultiplexer

- A decoder with an enable input is referred to as a decoder/demultiplexer.

- > The truth table of demultiplexer is the same with decoder.

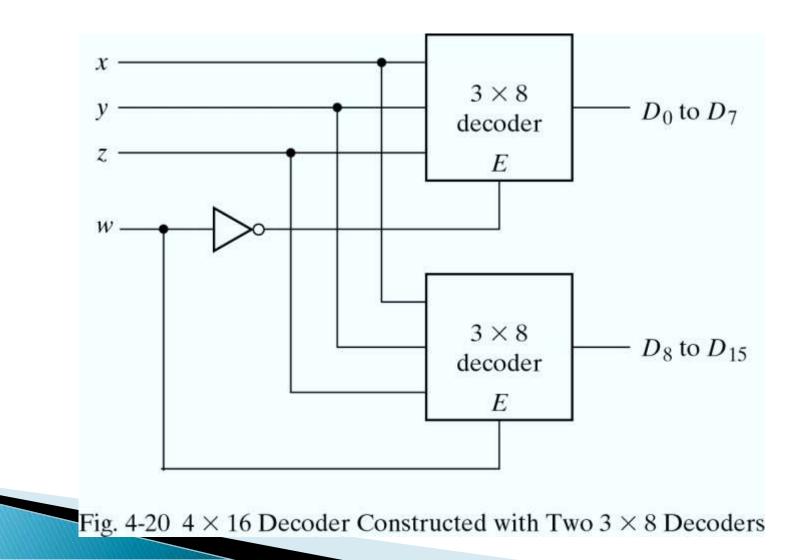

#### 3-to-8 decoder with enable implement the 4to-16 decoder

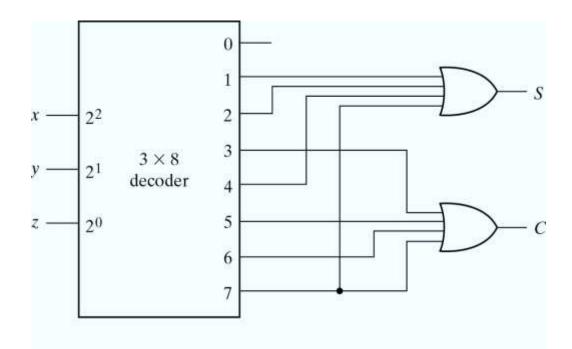

# Implementation of a Full Adder with a Decoder

From table 4-4, we obtain the functions for the combinational circuit in sum of minterms:

$S(x, y, z) = \sum(1, 2, 4, 7)$ C(x, y, z) =  $\sum(3, 5, 6, 7)$

Fig. 4-21 Implementation of a Full Adder with a Decoder

#### Encoders

- An encoder is the inverse operation of a decoder.

- We can derive the Boolean functions by table 4-7

$$z = D_1 + D_3 + D_5 + D_7$$

$$y = D_2 + D_3 + D_6 + D_7$$

$$x = D_4 + D_5 + D_6 + D_7$$

| Table 4-7                              |

|----------------------------------------|

| Truth Table of Octal-to-Binary Encoder |

| Inputs |       |       |       |       |       | Out   | puts  |   |   |   |

|--------|-------|-------|-------|-------|-------|-------|-------|---|---|---|

| $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | x | У | 2 |

| 1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 | 0 | C |

| 0      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0 | 0 | 1 |

| 0      | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0 | 1 | C |

| 0      | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0 | 1 | 1 |

| 0      | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1 | 0 | C |

| 0      | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1 | 0 | 1 |

| 0      | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1 | 1 | C |

| 0      | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1 | 1 | 1 |

# **Priority encoder**

- If two inputs are active simultaneously, the output produces an undefined combination. We can establish an input priority to ensure that only one input is encoded.

- Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; the output is the same as when  $D_0$  is equal to 1.

- The discrepancy tables on Table 4-7 and Table 4-8 can resolve aforesaid condition by providing one more output to indicate that at least one input is equal to 1.

# **Priority encoder**

V=0 $\rightarrow$ no valid inputs V=1 $\rightarrow$ valid inputs

X's in output columns represent don't-care conditions X's in the input columns are useful for representing a truth table in condensed form. Instead of listing all 16 minterms of four variables.

# Table 4-8 Truth Table of a Priority Encoder

|    | Inp | uts | (              | Dutput | s |   |

|----|-----|-----|----------------|--------|---|---|

| Do | D   | D2  | D <sub>3</sub> | x      | y | V |

| 0  | 0   | 0   | 0              | X      | X | 0 |

| 1  | 0   | 0   | 0              | 0      | 0 | 1 |

| X  | 1   | 0   | 0              | 0      | 1 | 1 |

| X  | X   | 1   | 0              | 1      | 0 | 1 |

| X  | X   | X   | 1              | 1      | 1 | 1 |

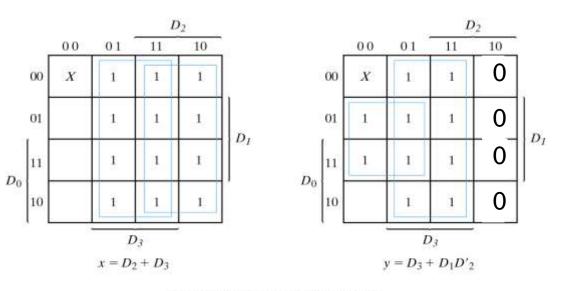

# 4-input priority encoder

Implementation of table 4-8

$\begin{aligned} \mathbf{x} &= \mathbf{D}_2 + \mathbf{D}_3 \\ \mathbf{y} &= \mathbf{D}_3 + \mathbf{D}_1 \mathbf{D'}_2 \\ \mathbf{V} &= \mathbf{D}_0 + \mathbf{D}_1 + \mathbf{D}_2 + \mathbf{D}_3 \end{aligned}$

Fig. 4-22 Maps for a Priority Encoder

Fig. 4-23 4-Input Priority Encoder

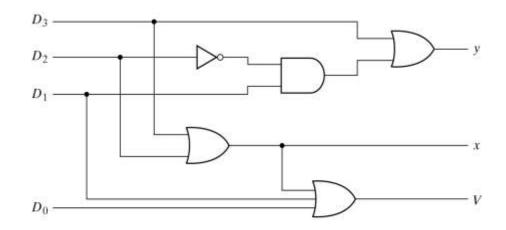

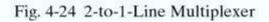

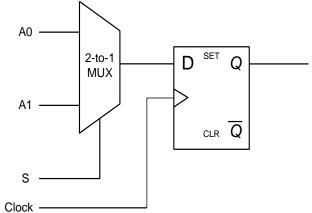

# Multiplexers

(a) Logic diagram

(b) Block diagram

# 4-to-1 Line Multiplexer

Y

Fig. 4-25 4-to-1-Line Multiplexer

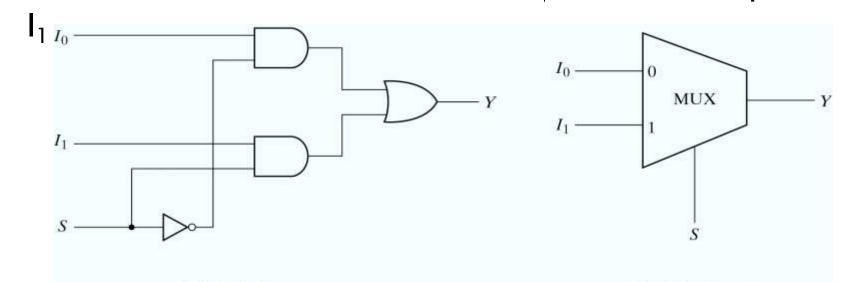

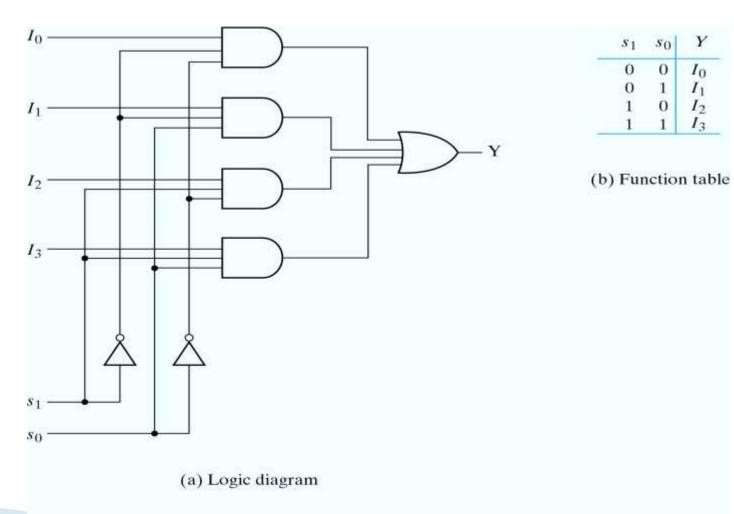

# Quadruple 2-to-1 Line Multiplexer

Multiplexer circuits can be combined with common selection inputs to provide multiple-bit selection logic. Compare with Fig4-24.

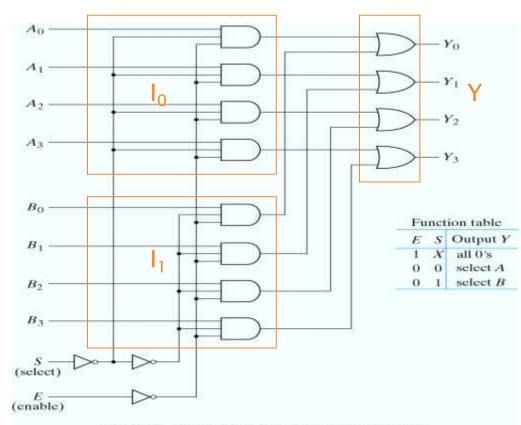

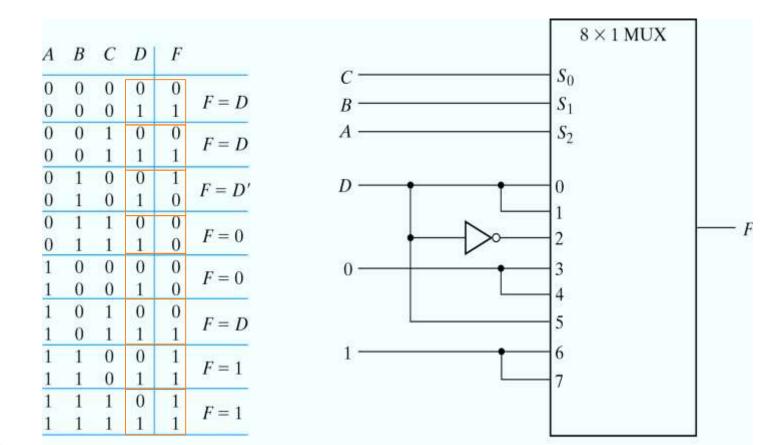

# **Boolean function implementation**

A more efficient method for implementing a Boolean function of n variables with a multiplexer that has n-1 selection inputs.

$$F(x, y, z) = \Sigma(1, 2, 6, 7)$$

#### 4-input function with a multiplexer

$F(A, B, C, D) = \Sigma(1, 3, 4, 11, 12, 13, 14, 15)$

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

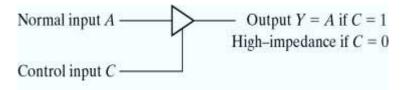

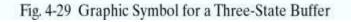

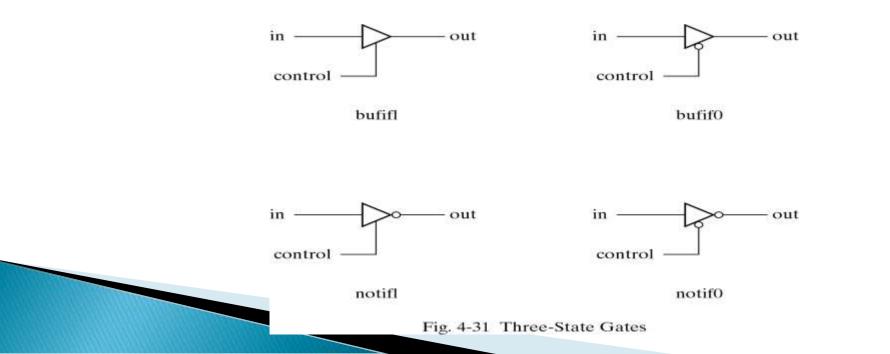

#### **Three-State Gates**

• A multiplexer can be constructed with three-state gates.

# Design methodologies

- There are two basic types of design methodologies: top-down and bottom-up.

- Top-down: the top-level block is defined and then the sub-blocks necessary to build the top-level block are identified.(Fig.4-9 binary adder)

- Bottom-up: the building blocks are first identified and then combined to build the top-level block.(Example 4-2 4-bit adder)

# Three state gates

Gates statement: gate name(output, input, control) >> bufif1(OUT, A, control);

A = OUT when control = 1, OUT = z when control = 0; >> notif0(Y, B, enable);

Y = B' when enable = 0, Y = z when enable = 1;

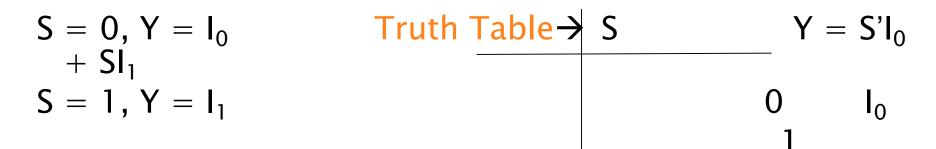

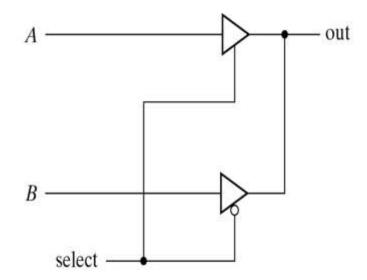

# 2-to-1 multiplexer

HDL uses the keyword tri to indicate that the output has multiple drivers.

module muxtri (A, B, select, OUT);

input A,B,select;

output OUT;

tri OUT;

bufif1 (OUT,A,select);

bufif0 (OUT,B,select);

endmodule

Fig. 4-32 2-to-1-Line Multiplexer with Three-State Buffers

IV UNIT

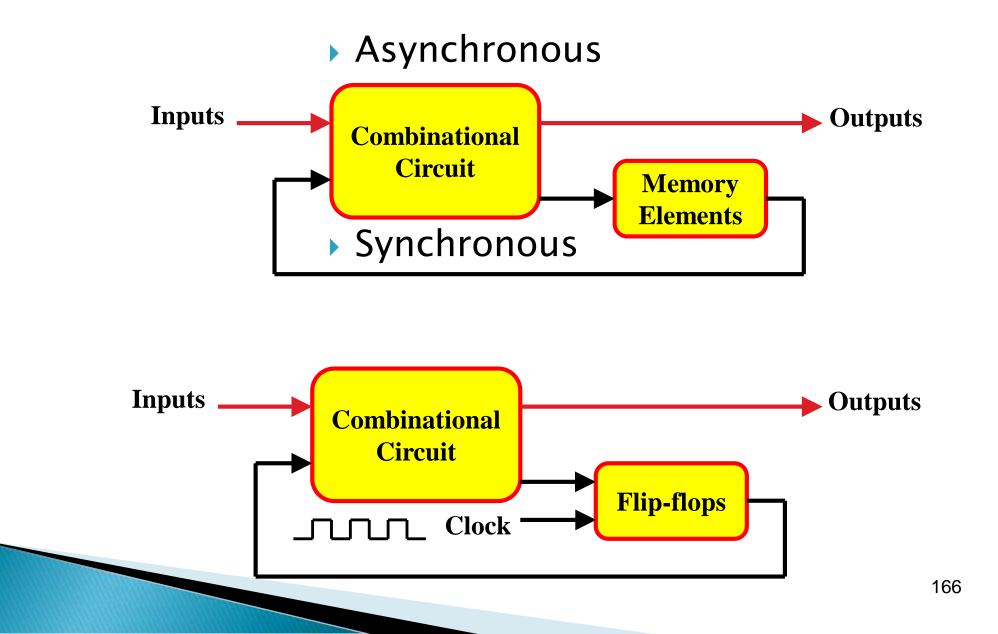

# Sequential Circuits

#### Sequential Circuits

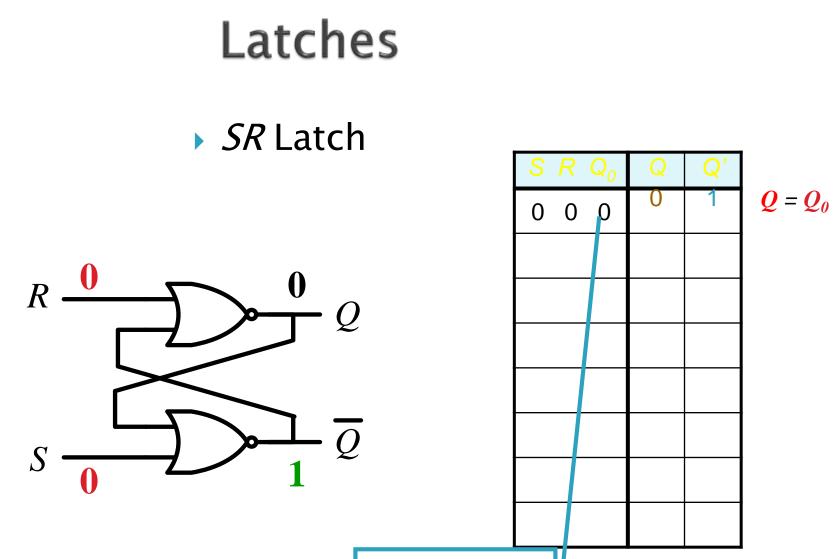

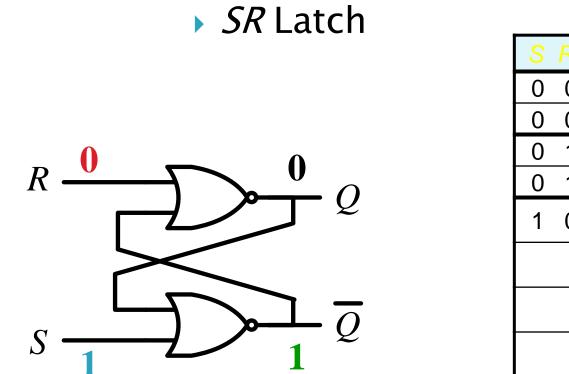

# FF vs. Latch

- Latches and flip-flops (FFs) are the basic building blocks of sequential circuits.

- latch: bistable memory device with level sensitive triggering (no clock), watches all of its inputs continuously and changes its outputs, independent of a clocking signal.

- flip-flop: bistable memory device with edge-triggering (with clock), samples its inputs, and changes its output only at times determined by a clocking signal.

**Initial Value**

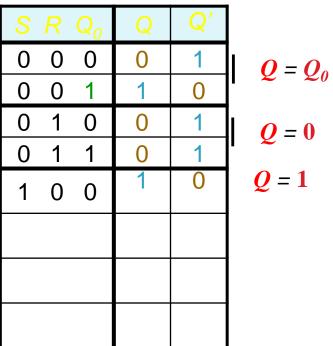

| $S R Q_0$ | Q | Q |                     |

|-----------|---|---|---------------------|

| 0 0 0     | 0 | 1 | $Q = Q_0$ $Q = Q_0$ |

| 0 0 1     | 1 | 0 | $Q = Q_0$           |

|           |   |   |                     |

|           |   |   |                     |

|           |   |   |                     |

|           |   |   |                     |

|           |   |   |                     |

|           |   |   |                     |

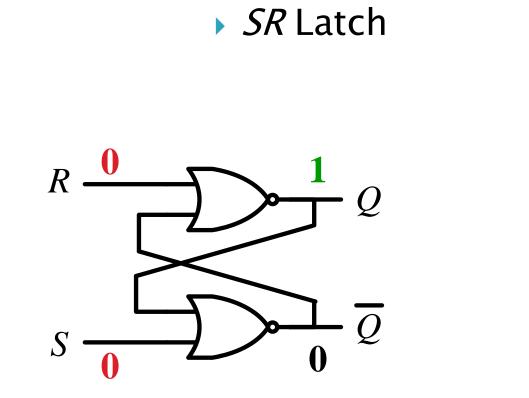

*SR* Latch

| S F | <b>ર Q</b> <sub>0</sub> | Q        | Q' |                     |

|-----|-------------------------|----------|----|---------------------|

| 0   | 0 0                     | 0        | 1  | <b>Q</b> = <b>Q</b> |

| 0   | 0 1                     | 1        | 0  |                     |

| 0   | 1 0                     | 0        | 1  | <i>Q</i> = 0        |

|     |                         |          |    |                     |

|     |                         |          |    |                     |

|     |                         |          |    |                     |

|     |                         |          |    |                     |

|     |                         | <b> </b> |    |                     |

|     |                         |          |    |                     |

$$Q = Q_0$$

*SR* Latch

| SRQ <sub>0</sub> | Q | Q |               |

|------------------|---|---|---------------|

| 0 0 0            | 0 | 1 | $Q = Q_0$     |

| 0 0 1            | 1 | 0 | -             |

| 0 1 0            | 0 | 1 | Q = 0 $Q = 0$ |

| 0 1 1            | 0 | 1 | Q = 0         |

|                  |   |   |               |

|                  |   |   |               |

|                  |   |   |               |

|                  |   |   |               |

|                  |   |   |               |

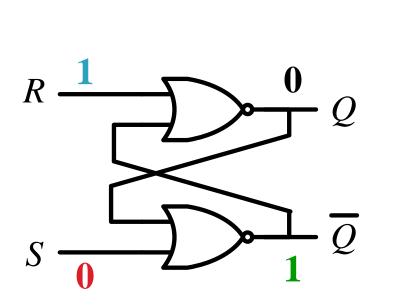

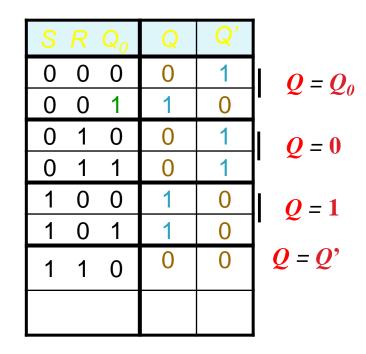

| S | R | $\mathbf{Q}_0$ | Q | Q |                |

|---|---|----------------|---|---|----------------|

| 0 | 0 | 0              | 0 | 1 | $Q = Q_0$      |

| 0 | 0 | 1              | 1 | 0 |                |

| 0 | 1 | 0              | 0 | 1 | <i>Q</i> = 0   |

| 0 | 1 | 1              | 0 | 1 | •              |

| 1 | 0 | 0              | 1 | 0 | Q = 1<br>Q = 1 |

| 1 | 0 | 1              | 1 | 0 | <i>Q</i> = 1   |

|   |   |                |   |   |                |

|   |   |                |   |   |                |

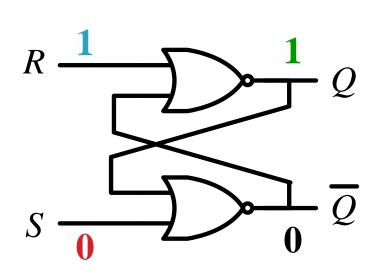

| S | R | $\mathbf{Q}_0$ | Q | Q |                       |

|---|---|----------------|---|---|-----------------------|

| 0 | 0 | 0              | 0 | 1 | $Q = Q_0$             |

| 0 | 0 | 1              | 1 | 0 |                       |

| 0 | 1 | 0              | 0 | 1 | <i>Q</i> = 0          |

| 0 | 1 | 1              | 0 | 1 |                       |

| 1 | 0 | 0              | 1 | 0 | <i>Q</i> = 1          |

| 1 | 0 | 1              | 1 | 0 |                       |

| 1 | 1 | 0              | 0 | 0 | <i>Q</i> = <i>Q</i> ' |

| 1 | 1 | 1              | 0 | 0 | Q = Q'                |

Invalid Set Reset

No change

No change Reset Set Invalid

Invalid Set Reset No change

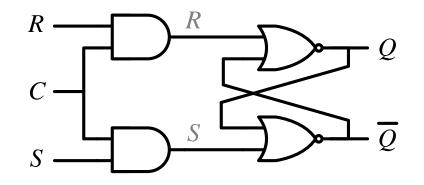

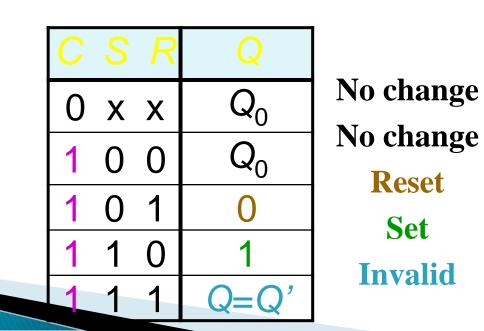

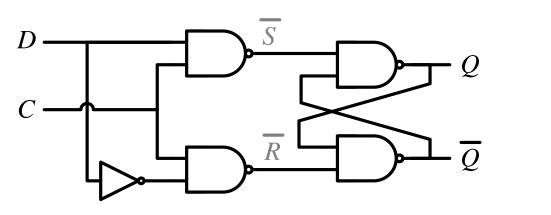

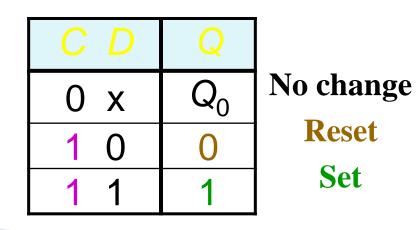

#### **Controlled Latches**

SR Latch with Control Input

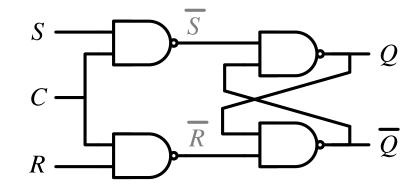

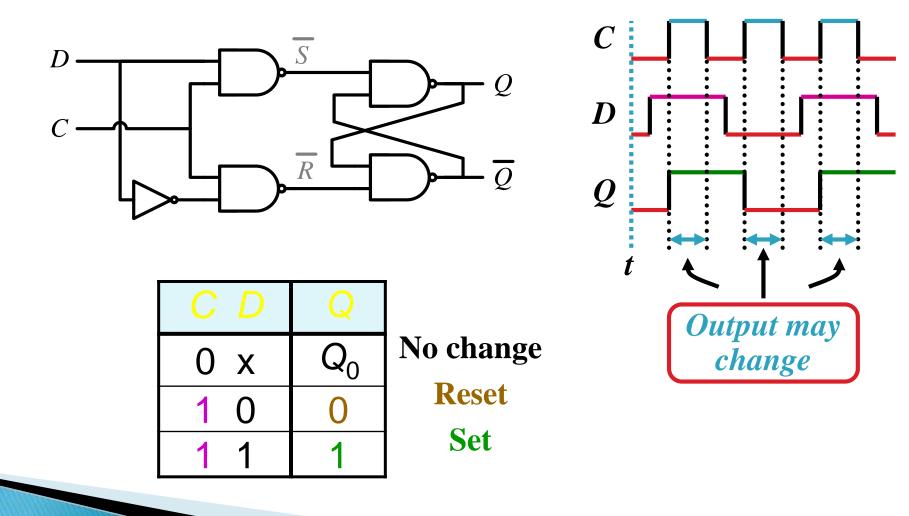

#### **Controlled Latches**

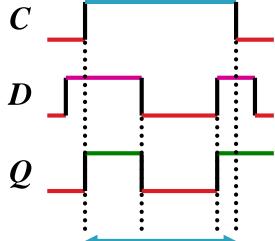

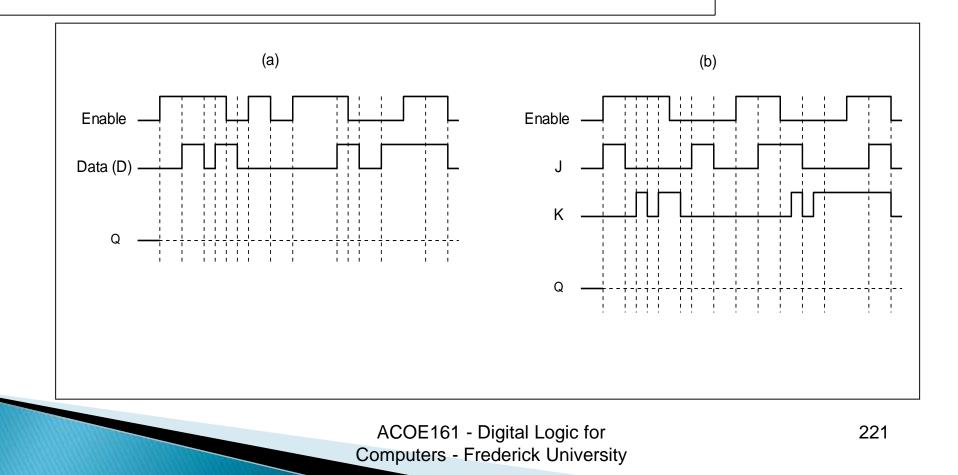

• D Latch (D = Data) Timing Diagram

#### **Controlled Latches**

• D Latch (D = Data) Timing Diagram

Output may

change

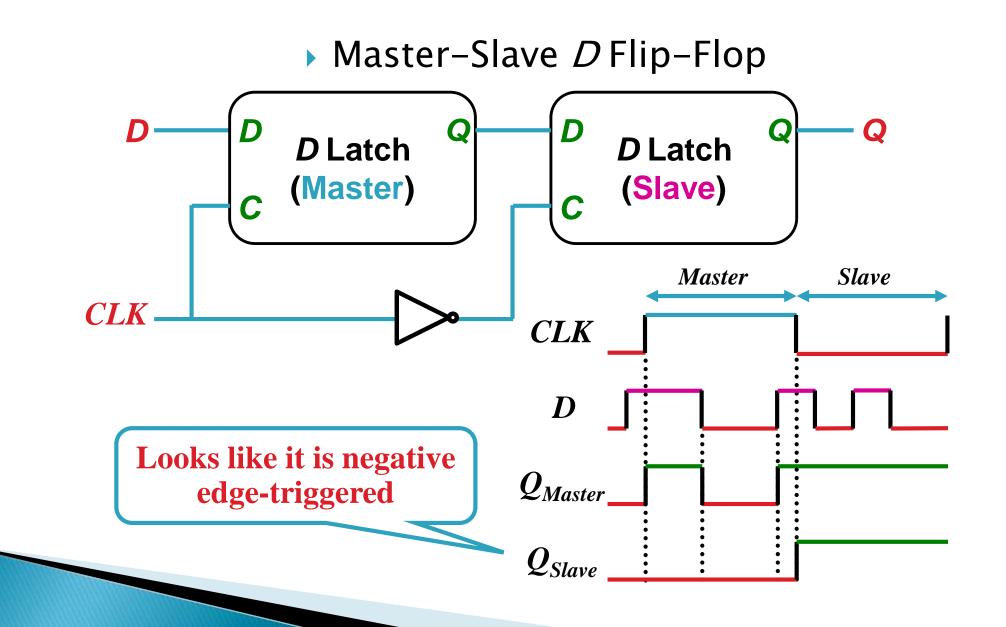

Controlled latches are level-triggered *C* Flip-Flops are edge-triggered Positive Edge Negative Edge

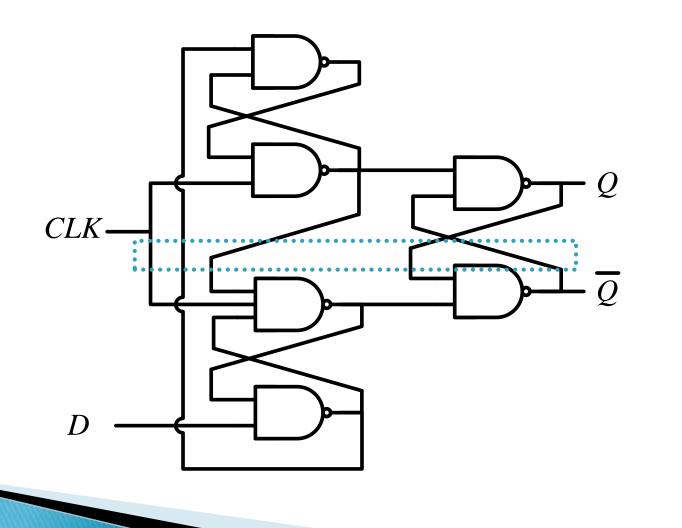

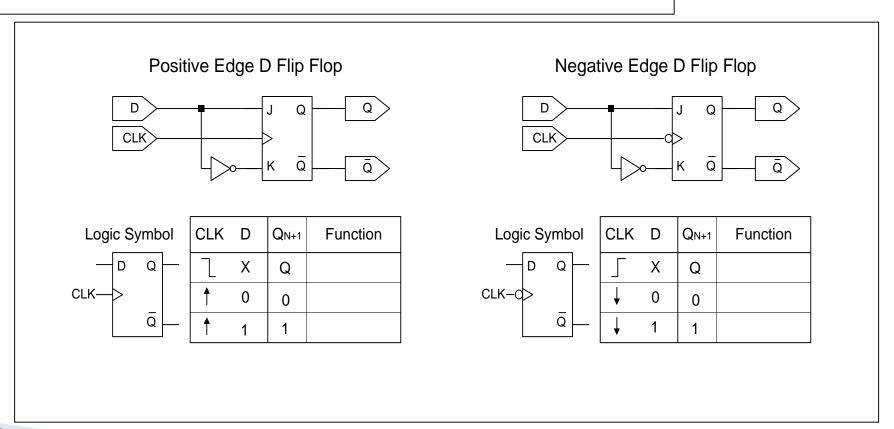

Edge-Triggered D Flip-Flop

Positive Edge

Negative Edge

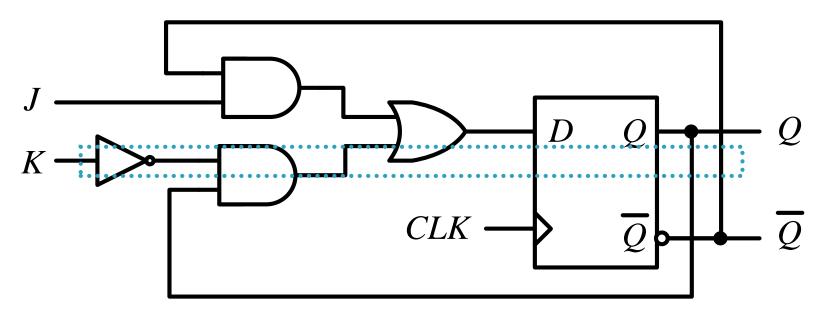

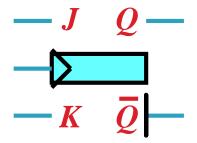

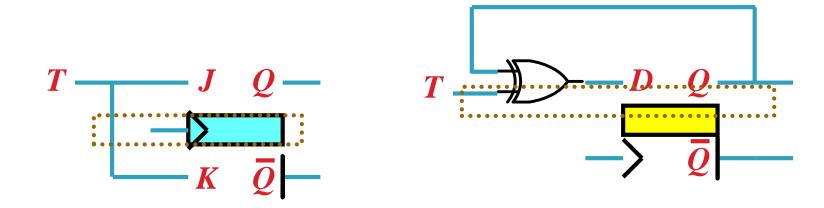

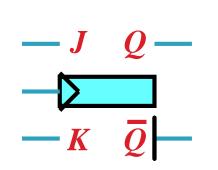

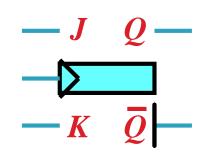

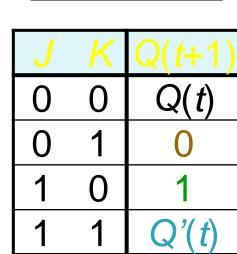

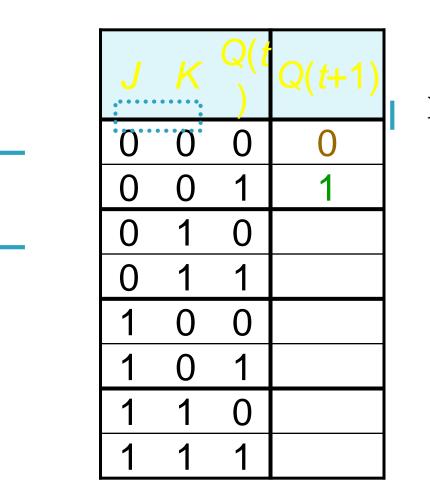

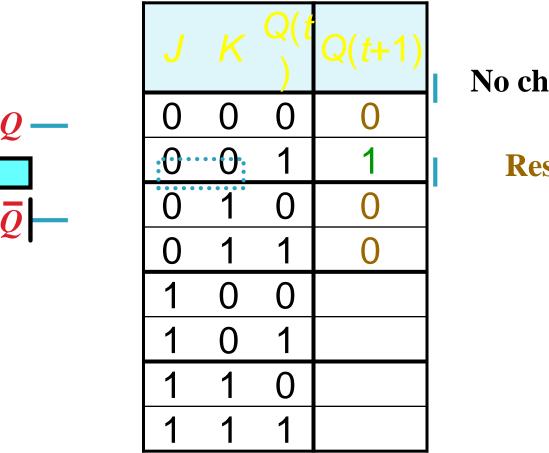

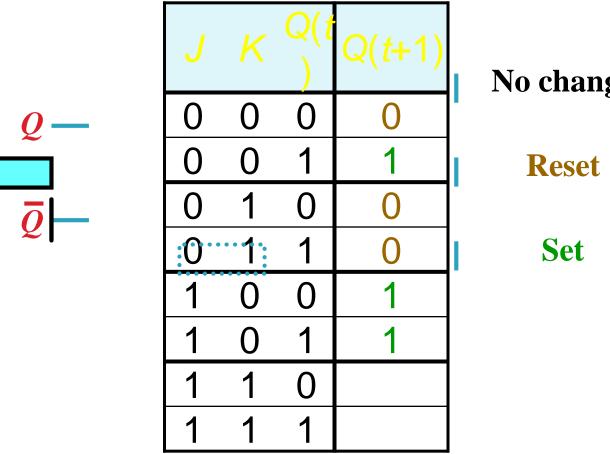

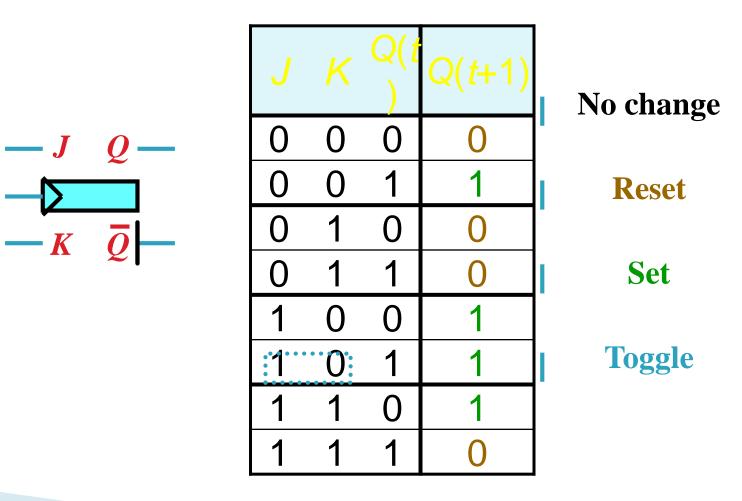

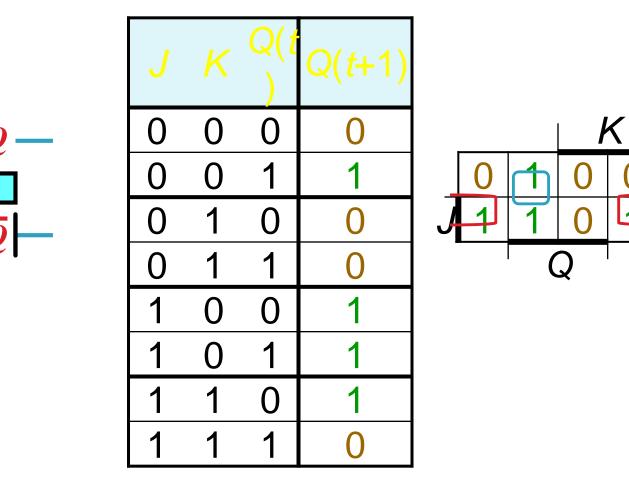

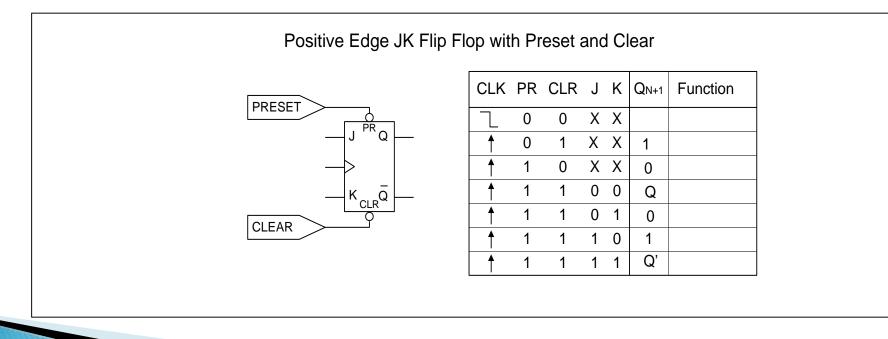

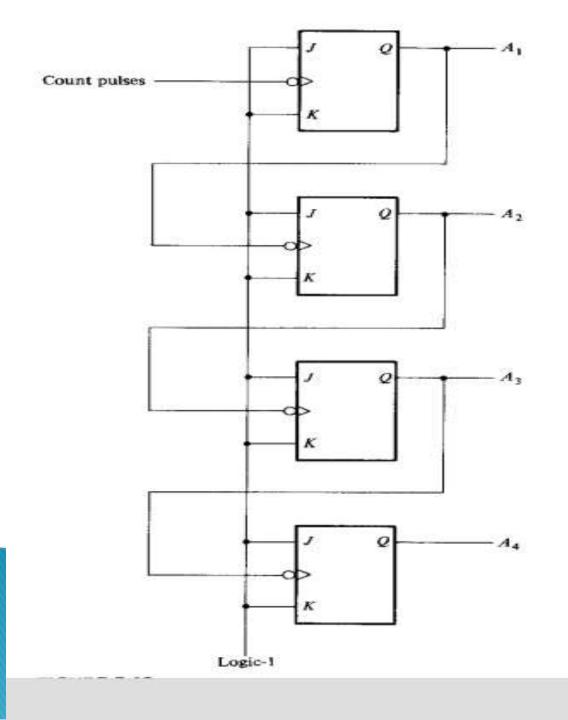

*JK* Flip–Flop

$$D = JQ' + K'Q$$

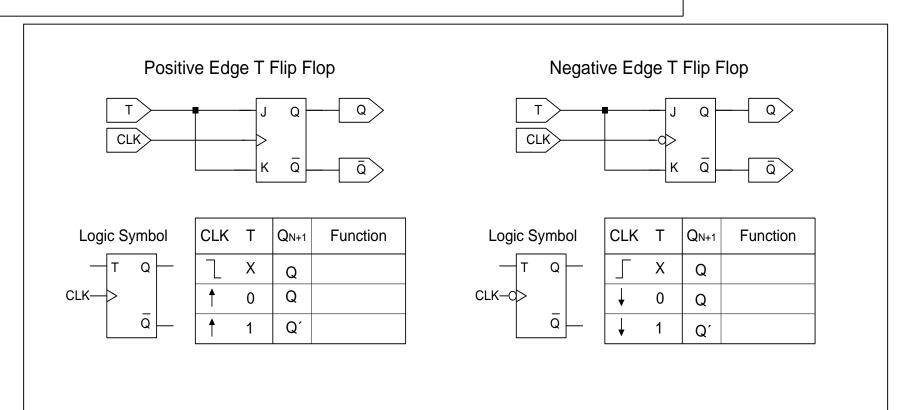

> TFlip-Flop

$$D = JQ' + K'Q$$

$$D = TQ' + T'Q = T \oplus Q$$

$$-T'Q$$

$$-T'Q$$

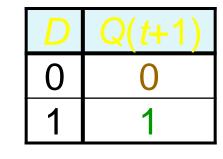

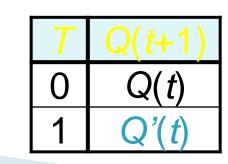

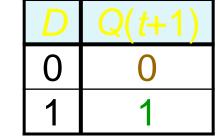

## Flip-Flop Characteristic Tables

-D Q  $\overline{\mathcal{Q}}$

Q

No change Reset Set Toggle

Reset

Set

No change Toggle

-D Q $\bar{Q}$

$$Q(t+1) = D$$

Q

$\overline{O}$

Q(t)

0

1

$$Q(t+1) = JQ' + K'Q$$

$$Q(t+1) = T \oplus Q$$

#### Analysis / Derivation

No change

Analysis / Derivation

No change

Reset

Analysis / Derivation

No change

Analysis / Derivation

Analysis / Derivation

**— K**

Q(t+1) = JQ' + K'Q

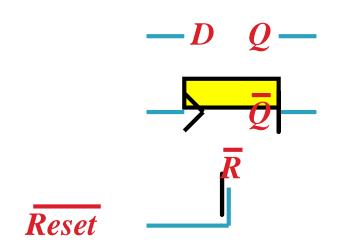

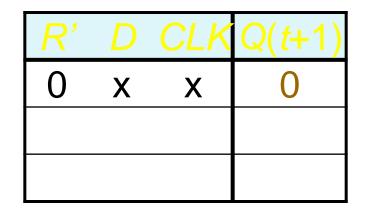

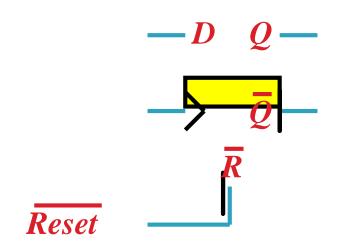

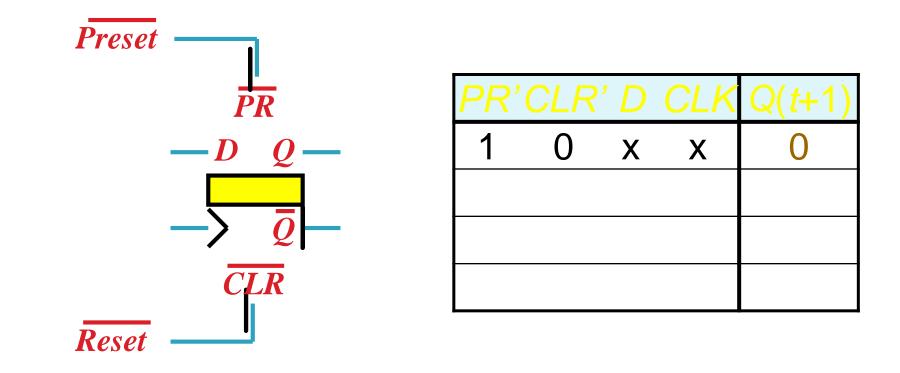

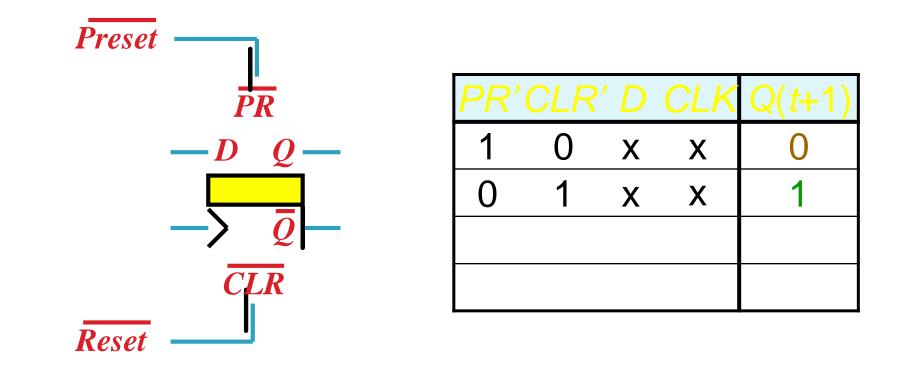

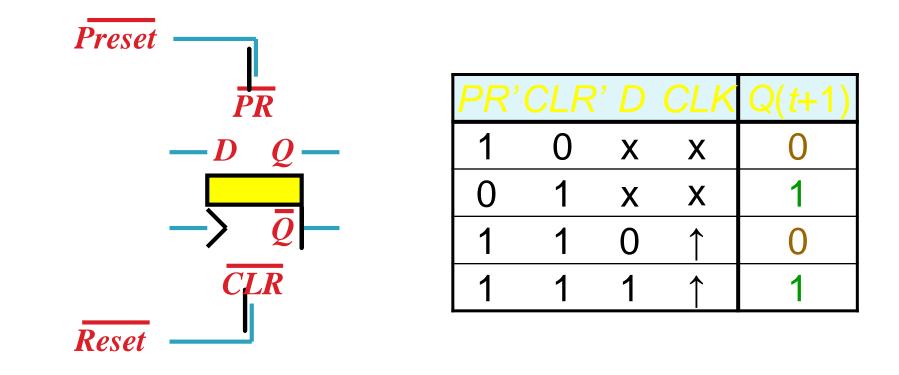

Asynchronous Reset

Asynchronous Reset

| R' | D | CLK           | Q( <i>t</i> +1) |

|----|---|---------------|-----------------|

| 0  | Х | Х             | 0               |

| 1  | 0 | $\rightarrow$ | 0               |

| 1  | 1 | $\uparrow$    | 1               |

Asynchronous Preset and Clear

Asynchronous Preset and Clear

Asynchronous Preset and Clear

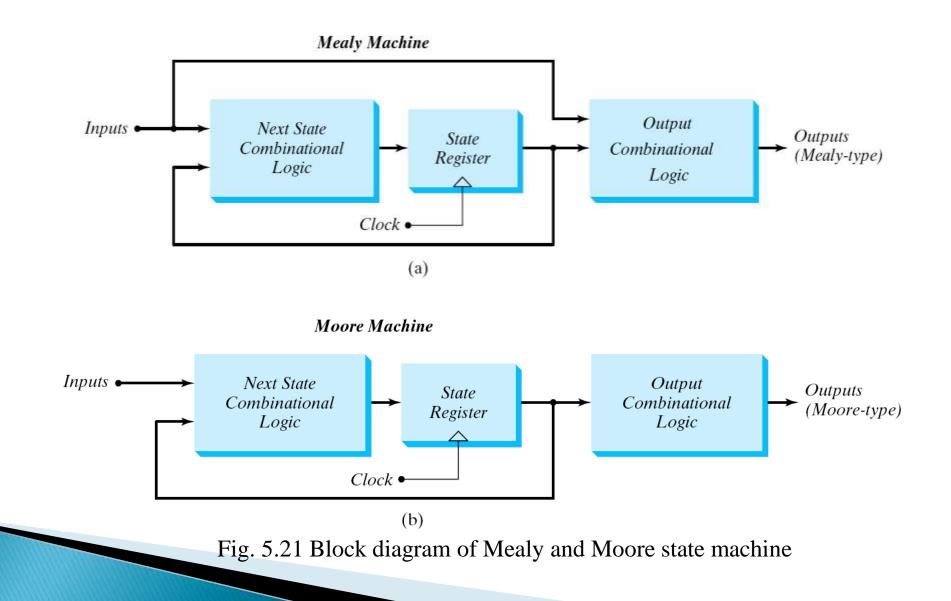

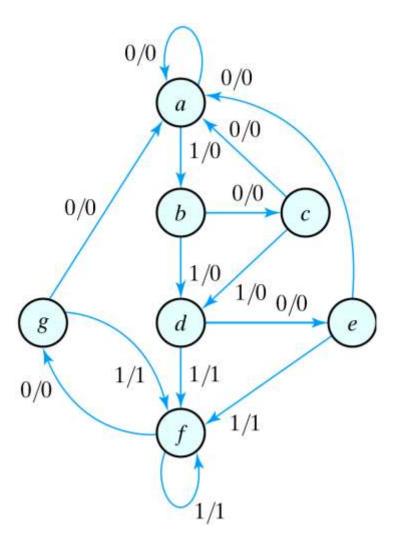

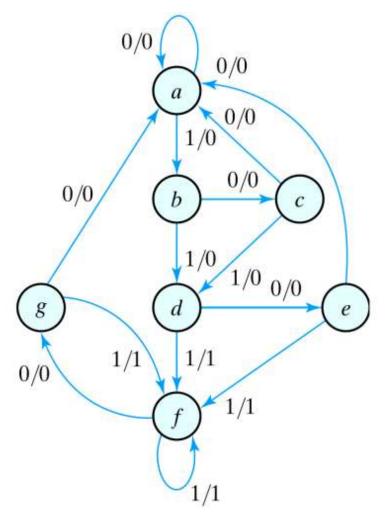

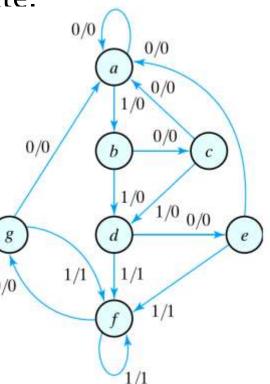

## Mealy and Moore Models

- The Mealy model: the outputs are functions of both the present state and inputs (Fig. 5–15).

- The outputs may change if the inputs change during the clock pulse period.

- The outputs may have momentary false values unless the inputs are synchronized with the clocks.

- The Moore model: the outputs are functions of the present state only (Fig. 5–20).

- The outputs are synchronous with the clocks.

#### Mealy and Moore Models

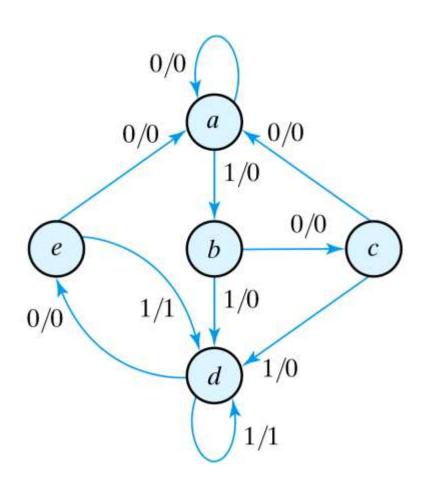

#### **State Reduction and Assignment**

- State Reduction Reductions on the number of flip-flops and the number of gates.

- A reduction in the number of states may result in a reduction in the number of flip-flops.

- An example state diagram showing in Fig. 5.25.

Fig. 5.25 State diagram

## **State Reduction**

State: a a b c d e f f g f g a

- Only the Input: 0 1 0 1 0 1 1 0 1 0 0

Only the Input-output output 0 0 0 0 0 1 1 0 1 0 0

sequences are important.

- Two circuits are equivalent

- Have identical outputs for all input sequences;

- The number of states is not important.

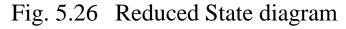

Fig. 5.25 State diagram

#### Equivalent states

- Two states are said to be equivalent

- For each member of the set of inputs, they give exactly the same output and send the circuit to the same state or to an equivalent state.

- One of them can be r

Table 5.6 State Table

|               | Next State |              | Output |              |

|---------------|------------|--------------|--------|--------------|

| Present State | x = 0      | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| a             | а          | b            | 0      | 0            |

| Ь             | С          | d            | 0      | 0            |

| с             | a          | d            | 0      | 0            |

| d             | е          | ſ            | 0      | 1            |

| е             | а          | ſ            | 0      | 1            |

| f             | g          | f            | 0      | 1            |

| g             | a          | ſ            | 0      | 1            |

# Reducing the state table e = g (remove g); d = f (remove f);

Table 5.7Reducing the State Table

|               | Next  | State        | Output |              |

|---------------|-------|--------------|--------|--------------|

| Present State | x = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| а             | а     | b            | 0      | 0            |

| b             | с     | d            | 0      | 0            |

| с             | а     | d            | 0      | 0            |

| d             | е     | f            | 0      | 1            |

| е             | а     | f            | 0      | 1            |

| f             | е     | f            | 0      | 1            |

#### • The reduced finite state machine

Table 5.8Reduced State Table

|               | Next S | State        | Output |              |

|---------------|--------|--------------|--------|--------------|

| Present State | x = 0  | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| а             | а      | Ь            | 0      | 0            |

| b             | С      | d            | 0      | 0            |

| с             | a      | d            | 0      | 0            |

| d             | e      | d            | 0      | 1            |

| е             | а      | d            | 0      | 1            |

State:aabcdeddedeaInput:010101101000Output:000001101000

- The checking of each pair of states for possible equivalence can be done systematically using Implication Table.

- The unused states are treated as don't-care condition ⇒ fewer combinational gates.

#### Table 5.8 Reduced State Table

|               | Next S | State        | Output |              |

|---------------|--------|--------------|--------|--------------|

| Present State | x = 0  | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| a             | а      | b            | 0      | 0            |

| Ь             | С      | d            | 0      | 0            |

| с             | a      | d            | 0      | 0            |

| d             | e      | d            | 0      | 1            |

| е             | a      | d            | 0      | 1            |

## Implication Table

| Present<br>State | Next State          |       | Output |       |

|------------------|---------------------|-------|--------|-------|

|                  | <b>x</b> = <b>0</b> | x = 1 | x = 0  | x = 1 |

| а                | :!                  | R.    | Ц      | Ц     |

| :                | s!                  | 2     | U      | I     |

| d                | P.                  | , i   | I.     |       |

| 1                | <b>1</b> *          | J.    | ()     | 0     |

## State Assignment

#### State Assignment

- To minimize the cost of the combinational circuits.

- Three possible binary state assignments. (*m* states need *n*-bits, where 2<sup>n</sup> > m)

#### Table 5.9

Three Possible Binary State Assignments

| State | Assignment 1,<br>Binary | Assignment 2,<br>Gray Code | Assignment 3,<br>One-Hot |

|-------|-------------------------|----------------------------|--------------------------|

| a     | 000                     | 000                        | 00001                    |

| Ь     | 001                     | 001                        | 00010                    |

| С     | 010                     | 011                        | 00100                    |

| d     | 011                     | 010                        | 01000                    |

| e     | 100                     | 110                        | 10000                    |

• Any binary number assignment is satisfactory as long as each state is assigned a unique number.

• Use binary assignment 1.

Table 5.10

Reduced State Table with Binary Assignment 1

|               | Next  | State        | Output |              |  |

|---------------|-------|--------------|--------|--------------|--|

| Present State | x = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |  |

| 000           | 000   | 001          | 0      | 0            |  |

| 001           | 010   | 011          | 0      | 0            |  |

| 010           | 000   | 011          | 0      | 0            |  |

| 011           | 100   | 011          | 0      | 1            |  |

| 100           | 000   | 011          | 0      | 1            |  |

## Sequential Digital Circuits

- Sequential circuits are digital circuits in which the outputs depend not only on the current inputs, but also on the previous state of the output.

- They basic sequential circuit elements can be divided in two categories:

- Level-sensitive (Latches)

- High-level sensitive

- Low–level sensitive

- Edge-triggered (Flip-flops)

- Rising (positive) edge triggered

- Falling (negative) edge triggered

- Dual-edge triggered

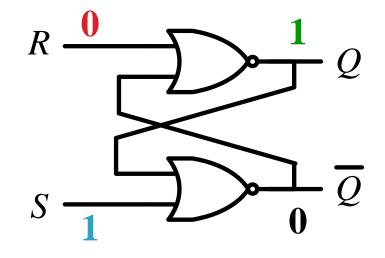

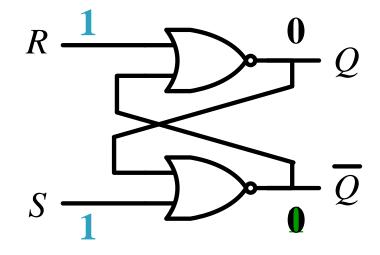

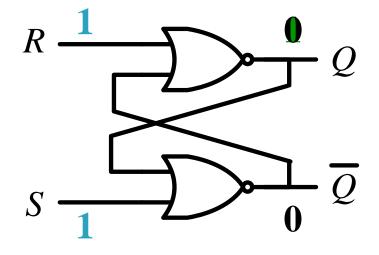

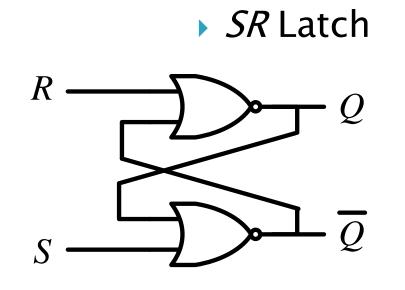

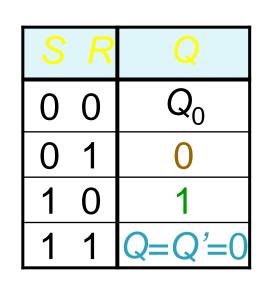

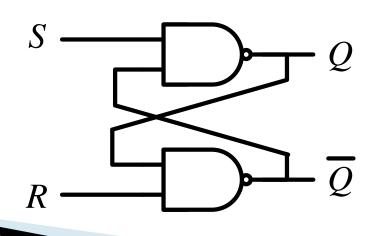

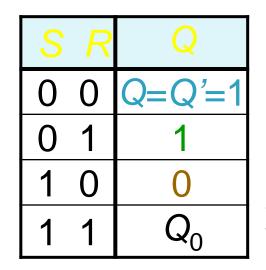

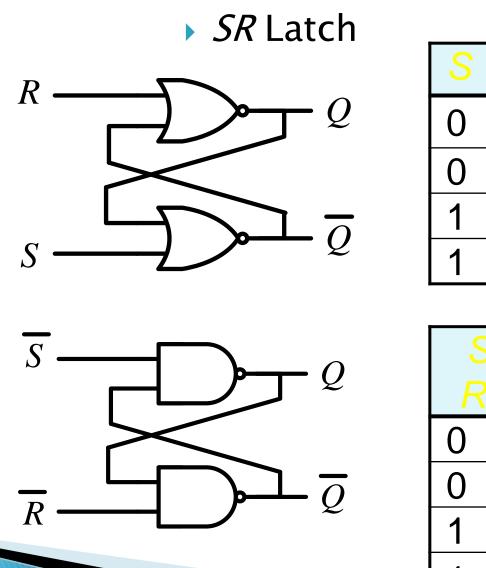

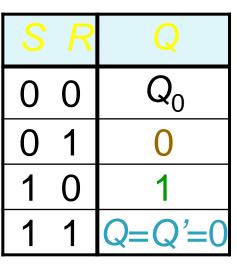

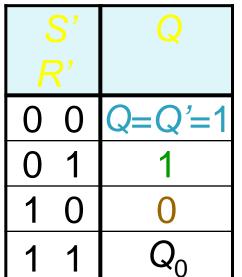

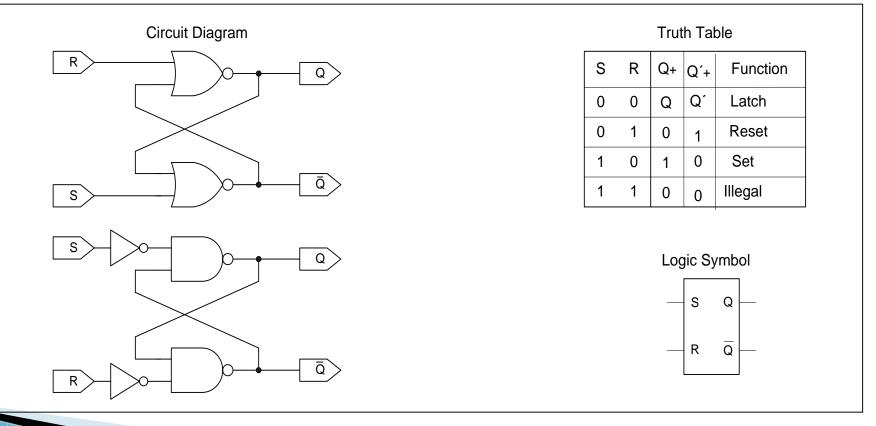

#### The Set/Reset (SR) Latch

The Set/Reset latch is the most basic unit of sequential digital circuits. It has two inputs (S and R) and two outputs outputs Q and Q'. The two outputs must always be complementary, i.e if Q is 0 then Q' must be 1, and vice-versa. The S input sets the Q output to a logic 1. The R input resets the Q output to a logic 0.

ACOE161 - Digital Logic for Computers - Frederick University

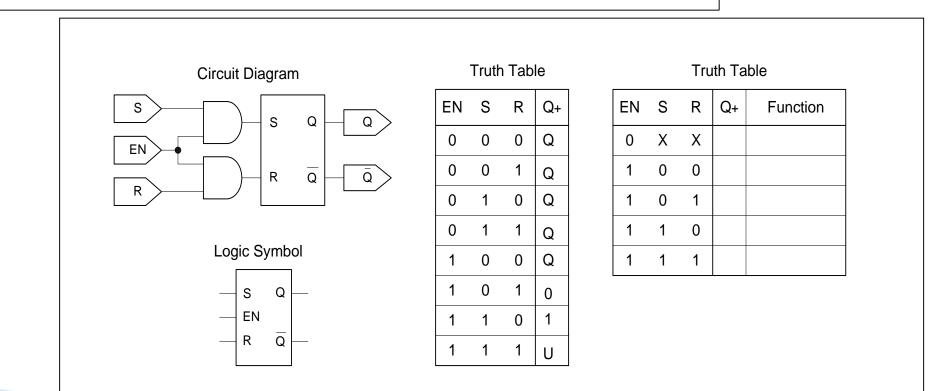

#### The Gated Set/Reset (SR) Latch

To be able to control when the S and R inputs of the SR latch can be applied to the latch and thus change the outputs, an extra input is used. This input is called the Enable. If the Enable is 0 then the S and R inputs have no effect on the outputs of the SR latch. If the Enable is 1 then the Gated SR latch behaves as a normal SR latch.

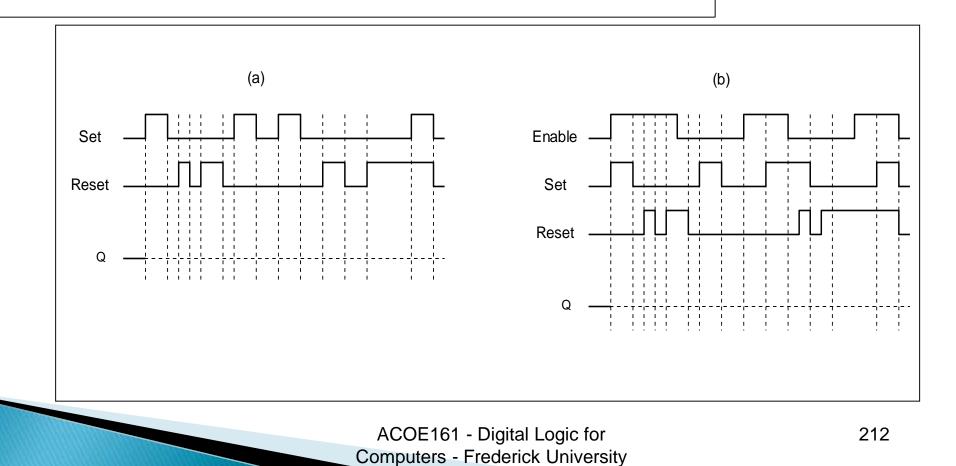

SR Latch :- Example

Complete the timing diagrams for :

- (a) Simple SR Latch

- (b) SR Latch with Enable input.

Assume that for both cases the Q output is initially at logic zero.

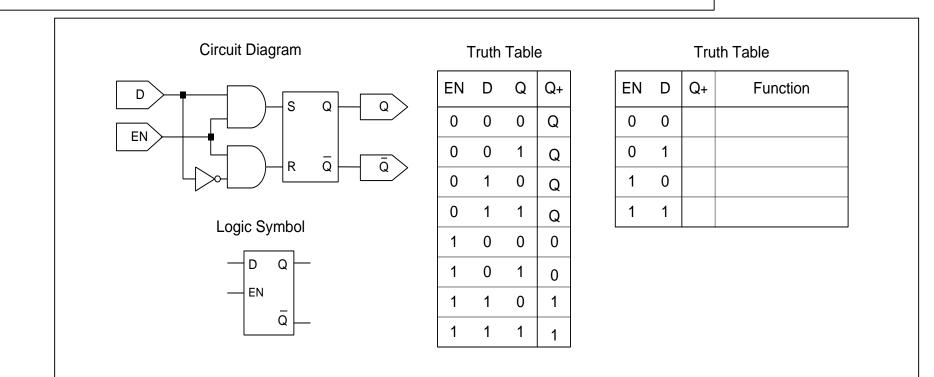

#### The Data (D) Latch

A problem with the SR latch is that the S and R inputs can not be at logic 1 at the same time. To ensure that this can not happen, the S and R inputs can by connected through an inverter. In this case the Q output is always the same as the input, and the latch is called the Data or D latch. The D latch is used in Registers and memory devices.

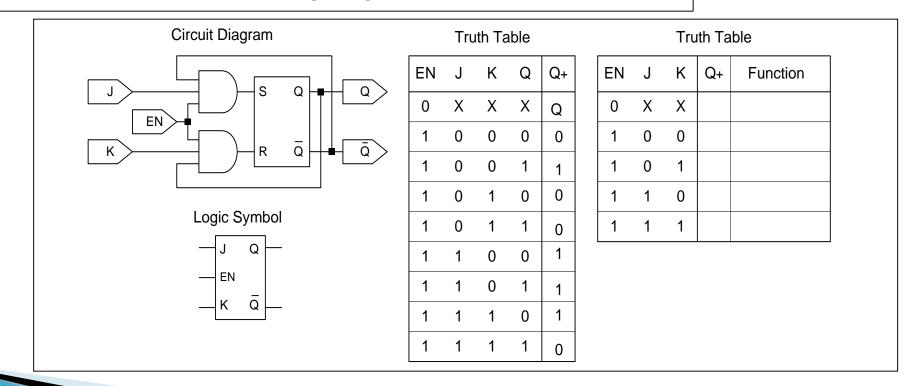

#### The JK Latch

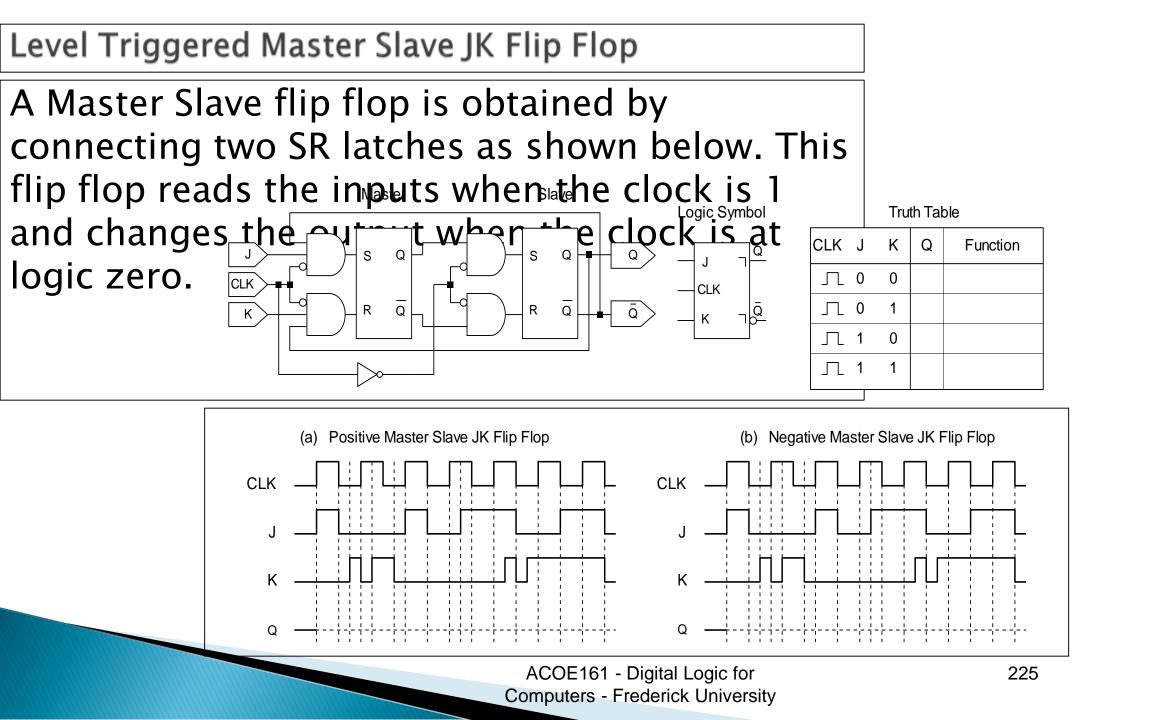

Another way to ensure that the S and R inputs can not be at logic 1 simultaneously, is to cross connect the Q and Q' outputs with the S and R inputs through AND gates. The latch obtained is called the JK latch. In the J and K inputs are both 1 then the Q output will change state (Toggle) for as long as the Enable 1, thus the output will be unstable. This problem is avoided by ensuring that the Enable is at logic 1 only for a very short time, using edge detection circuits.

#### Latches and Flip-Flops

- Latches are also called transparent or level triggered flip flops, because the change on the outputs will follow the changes of the inputs as long as the Enable input is set.

- Edge triggered flip flops are the flip flops that change there outputs only at the transition of the Enable input. The enable is called the Clock input.

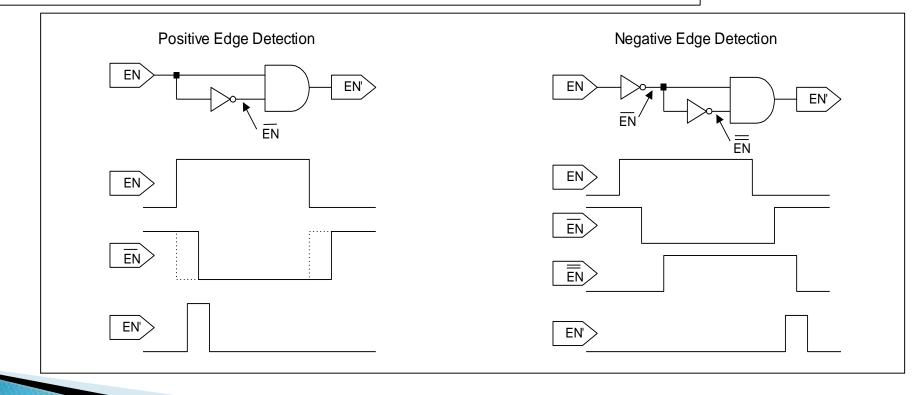

#### **Edge Detection Circuits**

Edge detection circuits are used to detect the transition of the Enable from logic 0 to logic 1 (positive edge) or from logic 1 to logic 0 (negative edge). The operation of the edge detection circuits shown below is based on the fact that there is a time delay between the change of the input of a gate and the change at the output. This delay is in the order of a few nanoseconds. The Enable in this case is called the Clock (CLK)

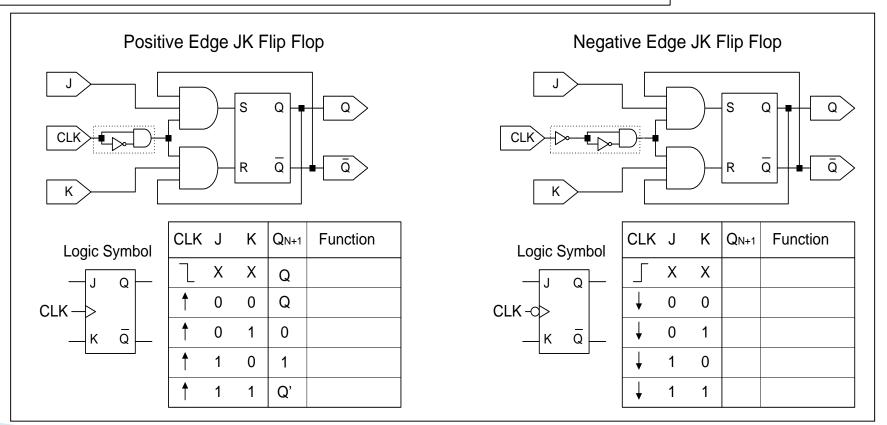

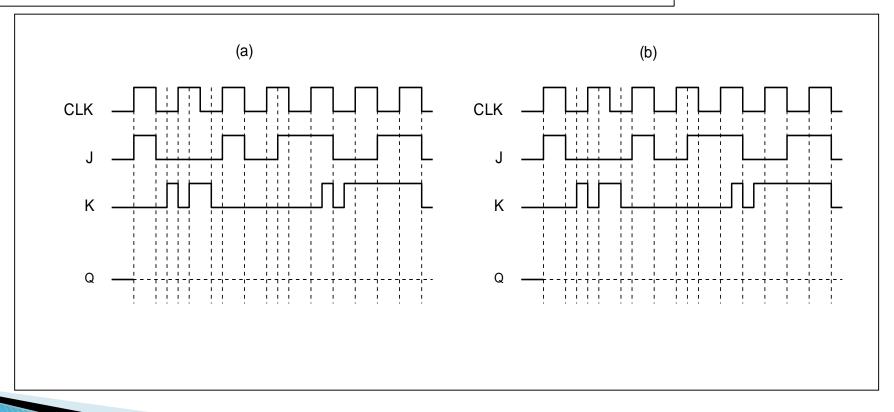

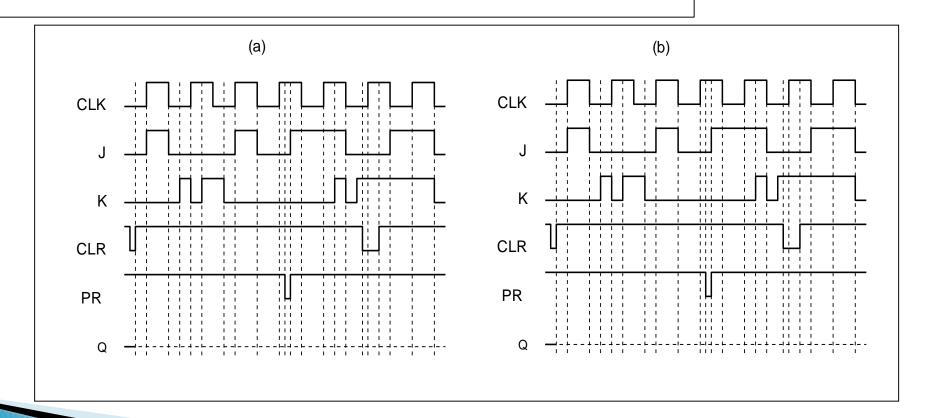

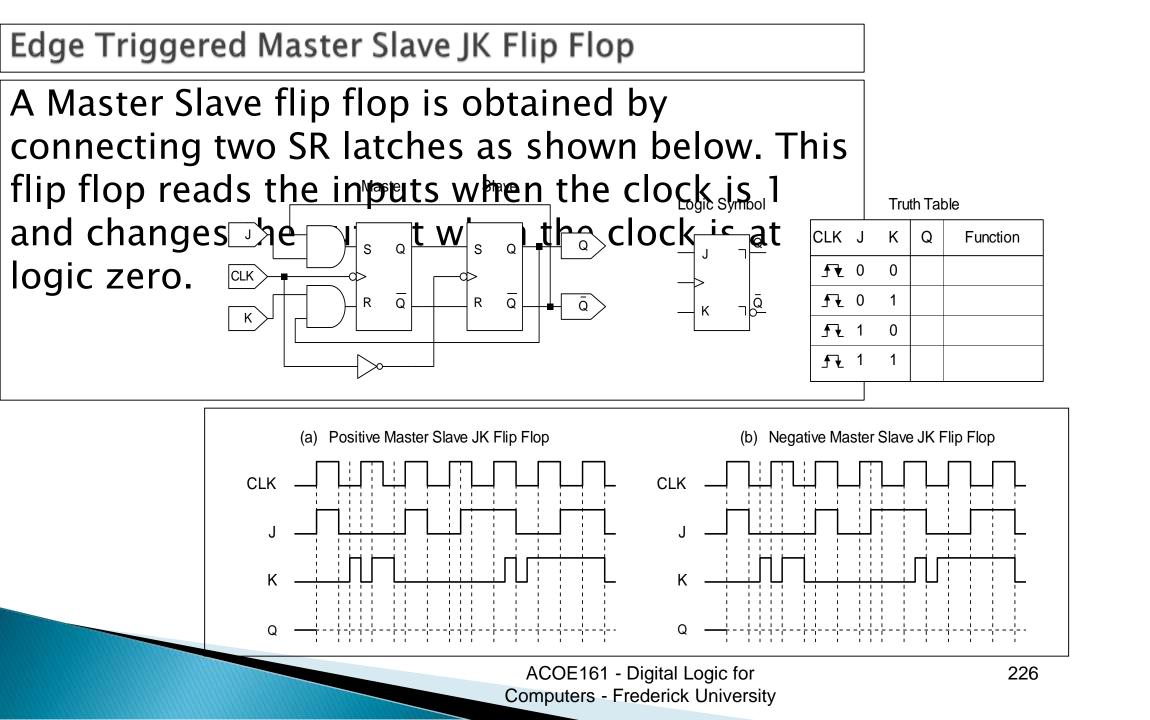

#### The JK Edge Triggered Flip Flop

The JK edge triggered flip flop can be obtained by inserting an edge detection circuit at the Enable (CLK) input of a JK latch. This ensures that the outputs of the flip flop will change only when the CLK changes (0 to 1 for +ve edge or 1 to 0 for -ve edge)

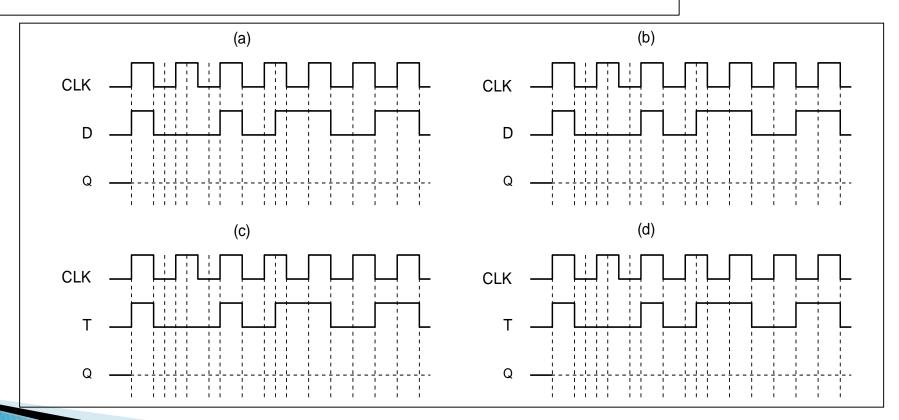

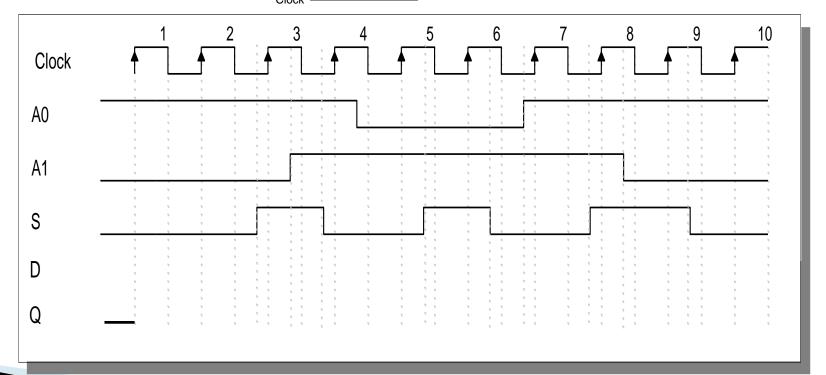

#### The D Edge Triggered Flip Flop